Superficies y vacío

ISSN: 1665-3521

alex@fis.cinvestav.mx

Sociedad Mexicana de Ciencia y Tecnología

de Superficies y Materiales A.C.

México

Huerta, J.; Murphy, R.; Díaz, A.; Torres, A.; Calleja, W.; Landa, M.

Fabricación y caracterización de inductores sobre silicio

Superficies y vacío, núm. 13, diciembre, 2001, pp. 44-49

Sociedad Mexicana de Ciencia y Tecnología de Superficies y Materiales A.C.

Distrito Federal, México

Disponible en: <http://www.redalyc.org/articulo.oa?id=94201311>

- ▶ Cómo citar el artículo

- ▶ Número completo

- ▶ Más información del artículo

- ▶ Página de la revista en [redalyc.org](http://redalyc.org)

redalyc.org

Sistema de Información Científica

Red de Revistas Científicas de América Latina, el Caribe, España y Portugal

Proyecto académico sin fines de lucro, desarrollado bajo la iniciativa de acceso abierto

## Fabricación y caracterización de inductores sobre silicio

J. Huerta-Chua<sup>1</sup>, R. Murphy-Arteaga<sup>2</sup>, A. Díaz-Sánchez<sup>3</sup>, A. Torres-Jacome<sup>4</sup>, W. Calleja-Arriaga<sup>5</sup>

M. Landa-Vázquez.

*Instituto Nacional de Astrofísica, Óptica y Electrónica

Coordinación de Electrónica, Tonantzintla, Puebla, México, 72840.*

En este artículo presentamos el diseño, la fabricación y caracterización de inductores pasivos sobre substratos de silicio. Estos inductores fueron fabricados utilizando una tecnología CMOS de 10 $\mu$ m de dimensión mínima, usando dos capas de aluminio, y SiO<sub>2</sub> como dieléctrico internivel. Se diseñaron, fabricaron y caracterizaron inductores poligonales y circulares, de cuatro y media y siete y media espiras. Las mediciones se realizaron con un Analizador Vectorial de Redes en el rango de 40 MHz a 5 GHz. Los resultados experimentales fueron comparados con la respuesta predicha del modelo eléctrico equivalente.

In this paper we present the design, fabrication and characterization of passive inductors on a silicon substrate. These inductors were fabricated using a 10 $\mu$ m minimum-feature CMOS process, with two aluminum layers and SiO<sub>2</sub> as the inter-level dielectric. Polygonal and circular inductors of four-and-a-half and seven-and-a-half turns were designed, fabricated and measured using a Vector Network Analyzer in the 40 MHz to 5 GHz range. Experimental results were compared to the predicted response of an equivalent electrical model.

**Descriptores:** Inductores; Fenómeno electromagnético; Circuitos integrados

**Keywords:** Inductors; Electromagnetic phenomena; Integrated circuits

### 1. Introducción

Los elementos pasivos juegan un papel muy importante en circuitos integrados (CIs) para telecomunicaciones. Cada uno de estos elementos presenta aplicaciones prácticas, especialmente en circuitos de radio frecuencia (RF), por sus características lineales, su más selectivo factor de calidad (Q), y por su bajo factor de ruido (NF). La investigación para la integración de inductores pasivos sobre un substrato conductorio empezó en la década de los 60s, pero fue hasta los 90s, cuando trabajos por Nguyen y Meyer [1], demostraron la posibilidad de realizarlos en circuitos integrados. A partir de entonces, muchos autores han reportado modificaciones en el diseño y en el proceso de fabricación de estos dispositivos [2-4], llevando esto a hacer mejoras significativas al inductor. En la actualidad, aún no se tiene un modelo eléctrico preciso para usarse en algún paquete para diseño de CIs comercial, por lo que es importante realizar un estudio de los parámetros eléctricos de los inductores integrados, para cuantificar los efectos de los elementos parásitos, especialmente en altas frecuencias, y obtener un modelo más apropiado para este tipo de componentes [5, 6]. Algunas aplicaciones de los inductores pasivos integrados se encuentran principalmente en amplificadores de bajo ruido (LNAs), osciladores controlados por voltaje (VCOs), mezcladores y filtros pasivos, entre otros [1, 5, 7-8].

Los inductores pasivos integrados son fabricados en tecnologías de Si y GaAs, usando espirales de metal (Al, Au, Cu), con diferentes geometrías (cuadrados, hexagonales, etc.). Entre las características más importantes de cualquier inductor destaca el que tenga un factor de calidad, Q, alto. Sin embargo, esta característica está limitada por componentes parásitas, como son las pérdidas resistivas del conductor y el acoplamiento capacitivo al substrato, entre otros. Componentes como éstos degradan el funcionamiento del inductor, y por lo

tanto deben ser reducidas dentro de las limitaciones propias de la estructura. Por ejemplo, los inductores fabricados en cobre presentan una resistencia serie menor a sus contrapartes de aluminio [9]. El diseño en espirales es otra manera de reducir las características no deseables, ya que esta técnica optimiza el área ocupada, disminuyendo el valor de la capacitancia parásita.

Actualmente, los inductores más comúnmente utilizados son los de espiras cuadradas, principalmente por su sencilla fabricación, pero se han reportado inductores poligonales de seis y ocho lados [10, 11]. Por otro lado, autores como Niknejad [12] y Lee [13], han reportado trabajos sobre la caracterización y modelado de inductores coplanares con geometrías de más de ocho lados, hasta llegar a la espiral circular.

En este trabajo reportamos el diseño, modelado, fabricación y caracterización de inductores poligonales y circulares. El modelo eléctrico se presenta en la Sección II; el factor de calidad se define en la Sección III; la Sección IV explica el diseño y el proceso de fabricación. Los resultados experimentales se discuten en la Sección V, y las conclusiones generales derivadas del trabajo se anotan en la Sección VI.

### 2. Modelo Eléctrico

En un inductor pasivo integrado, las fuentes más importantes de pérdidas son tres: La resistencia del conductor, el acoplamiento capacitivo al substrato, y la potencia disipada en el substrato por corrientes de remolino.

#### Variación Resistiva.

La mayoría de los inductores son fabricados usando capas de metal, generalmente aluminio, cobre o aleaciones. La resistencia del espiral ( $\Omega$ ) es directamente proporcional a la

<sup>1</sup>jhuerta@susu.inaoep.mx, <sup>2</sup>rmurphy@ieee.org, <sup>3</sup>adiazsan@inaoep.mx, <sup>4</sup>atorres@inaoep.mx, <sup>5</sup>wcalleja@inaoep.mx

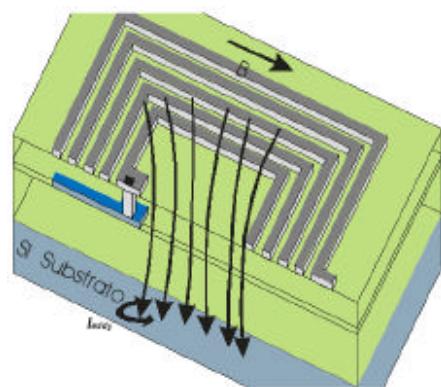

Figura 1. Vista 3D de un inductor de espiras cuadradas donde se esquematizan las corrientes inducidas al substrato de silicio.

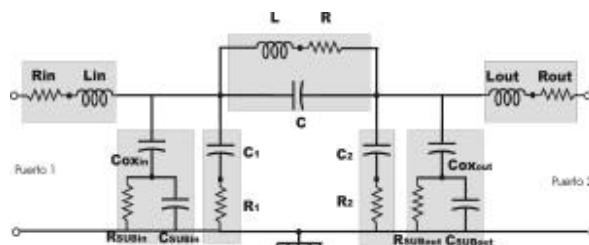

Figura 2. Modelo eléctrico para un inductor coplanar.

resistividad del metal y la geometría de la línea:

$$R = \rho \left( \frac{l}{\tau W} \right) = \left( \frac{\rho}{\tau} \right) \left( \frac{l}{W} \right) = R_S \left( \frac{l}{W} \right) \quad (1)$$

Donde  $\rho$  es la resistividad del material en  $\Omega \text{cm}$ ;  $\tau$  es el espesor en cm;  $l$  es la longitud del material en  $\mu\text{m}$ ;  $W$  es el ancho del material, en  $\mu\text{m}$ ; y  $R_S$  es la resistencia por cuadro, en  $\Omega/\text{cuadro}$ . Esta resistencia es la medible en corriente directa (CD), pero para altas frecuencias, la distribución de la corriente en la capa de metal cambia con frecuencia conforme a la profundidad de piel. Una expresión válida para altas frecuencias es [13]:

$$R = \left( \frac{\rho}{\delta(1 - e^{-z/\delta})} \right) \left( \frac{l}{W} \right) \quad (2)$$

Donde  $z$  es la distancia en el material y  $\delta$  es la profundidad de piel, para un buen conductor dada aproximadamente por [14]:

$$\delta \approx \sqrt{\frac{2\rho}{\omega\mu_0}} \quad (3)$$

Aquí,  $\omega$  es la frecuencia angular (rad/seg), y  $\mu_0$  es la permeabilidad del espacio libre ( $4\pi \times 10^{-7} \text{ H/m}$ ).

### Acoplamiento Capacitivo.

El acoplamiento capacitivo entre el conductor y el substrato

es la segunda fuente de pérdidas. Su valor se puede aproximar usando la expresión para un capacitor de placas paralelas:

$$C \approx \epsilon \frac{A}{h} \approx \epsilon \frac{W \cdot l}{h} \quad (4)$$

En ésta,  $C$  es la capacitancia, en F (o pF);  $\epsilon$  es la permitividad del material dieléctrico entre el conductor y el substrato, en F/cm;  $A$  es el área del capacitor en  $\text{cm}^2$ ;  $W$  el ancho de la placa en cm;  $l$  el largo de la placa en cm; y  $h$  es la separación entre el conductor y el substrato, también en cm. El área,  $A$ , es únicamente la ocupada por el conductor. En el inductor también existe un acoplamiento capacitivo entre el puerto de entrada y de salida, conocido como capacitancia serie. En el modelo eléctrico del inductor, se considera como un capacitor entre el puerto de entrada y el de salida.

### Potencia Disipada en el Substrato.

La tercera contribución de importancia es la potencia que se disipa en el substrato por la Ley de Faraday. Al tener un campo magnético variante con el tiempo, se induce un campo eléctrico tanto en las espiras como en el substrato. Este campo inducido genera corrientes parásitas, conocidas como corrientes de remolino o de vórtice. Una representación esquemática de este efecto se muestra en la Figura 1.

Estas pérdidas de potencia se pueden modelar eléctricamente, en conjunto con el acoplamiento al substrato, al incluir un capacitor en serie con un resistor del conductor al substrato, como se muestra en el modelo eléctrico de la Figura 2, con los capacitores  $C_1$  y  $C_2$  y las resistencias  $R_1$  y  $R_2$ .

### Modelo para inductores coplanares.

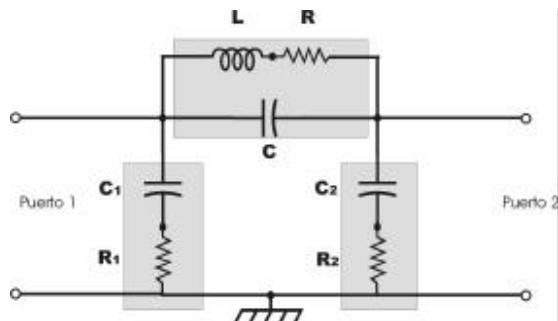

El modelo completo de un inductor coplanar integrado como una red de dos puertos se muestra en la Figura 2. Este modelo incluye las plataformas de contacto y las líneas de interconexión necesarias para llevar a cabo las mediciones eléctricas. Las plataformas de contacto se pueden modelar aproximadamente por la combinación  $C_{OXin}$ ,  $R_{SUBin}$ ,  $C_{SUBin}$  y  $C_{OXout}$ ,  $R_{SUBout}$ , y  $C_{SUBout}$ . Ya que éstas son grandes comparadas con el dispositivo bajo prueba, es necesario considerar su efecto en los datos experimentales para eliminarlo de las mediciones del inductor. Similarmente, las pistas de interconexión haciendo contacto con el inductor representan una resistencia ( $R_{in}$ ,  $R_{out}$ ) y una inductancia adicional ( $L_{in}$ ,  $L_{out}$ ), que hay que eliminar para tener la medición real del inductor. No es necesario cuantificar estas componentes ya que se eliminan con un procedimiento de "des-incrustación" de mediciones [15]. Una vez haciendo esto, el modelo equivalente del inductor integrado se reduce al mostrado en la Figura 3. Este modelo es un equivalente  $\pi$ , por lo que los valores de interés se pueden obtener sencillamente de los datos experimentales.

Figura 3. Modelo compacto de un inductor coplanar.

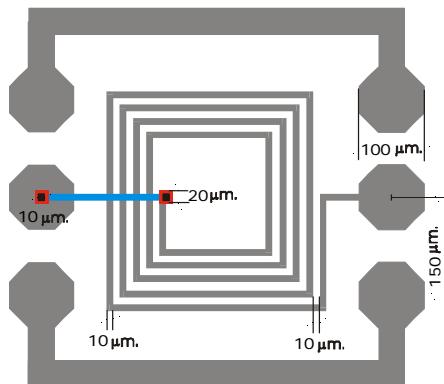

Figura 4. Patrón geométrico de un inductor cuadrado de 4.5 espiras

Si los datos medidos (Parámetros S) se transforman a Parámetros Y, por ejemplo, entonces la combinación serie de la inductancia (L) y la resistencia (R) en paralelo con la capacitancia (C), se puede expresar:

$$Y = Y_R + jY_I \quad (5)$$

Donde  $j = \sqrt{-1}$  y  $Y_R$  y  $Y_I$  son las partes real e imaginaria respectivamente. Éstas están dadas por:

$$Y_R = \frac{R}{R^2 + \omega^2 L^2} \quad (6)$$

$$Y_I = \omega \frac{CR^2 - L + \omega^2 CL^2}{R^2 + \omega^2 L^2} \quad (7)$$

Comparando los datos experimentales a este modelo, los valores de R, C y L se pueden obtener por optimización multivariable [16].

### Factor de Calidad Q

Para aplicaciones en RF, una de las figuras de mérito más importantes del inductor es su factor de calidad, Q. Este factor es fuertemente dependiente de la disipación de

energía en el inductor, atribuible a componentes parásitas. En la literatura existen varias definiciones para este parámetro, entre las que destacan [13]:

$$Q = \omega \frac{E_{A-MAX}}{P_{DIS}} \quad (8)$$

En ésta,  $E_{A-MAX}$  es la energía máxima almacenada en los campos eléctrico y magnético, y  $P_{DIS}$  es la potencia disipada en el mismo tiempo.

Sin embargo, la definición más práctica en este caso relaciona las partes real e imaginaria de la admitancia de entrada del Puerto 1:

$$Q = - \left[ \frac{Y_{11I}}{Y_{11R}} \right] \quad (9)$$

### 3. Diseño y Fabricación

El esquema básico de diseño para todas las estructuras se muestra en la Figura 4. Las plataformas de contacto se diseñaron para un sistema de puntas de prueba GSG (Tierra-Señal-Tierra) de 150 μm de separación. La terminal de Señal en cada puerto se conectó a una de las terminales del inductor.

El ancho mínimo de las pistas, el espacio entre espiras, y las dimensiones de los contactos, se apegaron a las reglas de diseño de la tecnología CMOS del Laboratorio de Microelectrónica del INAOE.

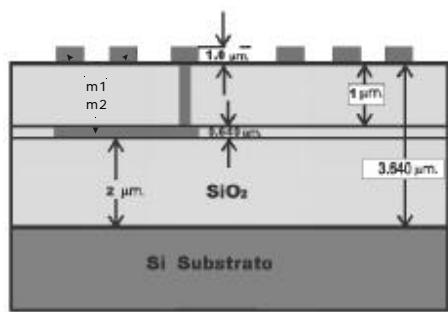

Los inductores fueron fabricados usando dos capas de metal. Se utilizaron 3 obleas tipo N, de orientación (100) y resistividad entre 2.38 y 3.85 Ωcm. Un corte seccional de las estructuras se muestra en la Figura 5. La interconexión interna de la espira se hizo con el primer nivel de metal (m1), conectado usando una vía a la segunda capa de metalización (m2), que se usó para las espiras y la conexión al puerto de salida.

Para tener la misma tierra de referencia en ambos puertos, las regiones de contactos en el substrato fueron implantadas con fósforo hasta alcanzar una concentración superficial de  $5 \times 10^{19} \text{ cm}^{-3}$ . En seguida, se creció dióxido de silicio térmicamente en ambiente de vapor de agua, a  $T=1,100^\circ\text{C}$  por 40min, obteniendo un espesor de 5,000 Å. La región de la vía se grabó y se llenó de aluminio. Sobre esta capa de óxido se depositó una película de  $\text{SiO}_2$  por CVD, de 6,500 Å de espesor. Se grabó y llenó la vía, y se depositó el primer nivel de metal, hasta un espesor de 6,500 Å. Sobre este nivel se depositó otra película de  $\text{SiO}_2$ , con un espesor de 9,800 Å. Se grabó y llenó la vía, y se depositó el segundo nivel de metal, con un espesor de 1 μm.

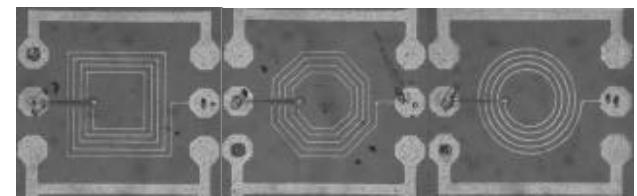

Las microfotografías de algunos de los inductores fabricados se presentan en la Figura 6. En este caso, corresponden a inductores cuadrados, octogonales y circulares de 4 y media espiras.

### 4. Mediciones

Los inductores fabricados fueron primero caracterizados en CD para probar continuidad de las pistas y medir la

Figura 5. Vista transversal de un inductor fabricado sobre silicio.

Figura 6. Fotografías de inductores fabricados: espiras cuadradas, octagonales y circulares de 4.5 vueltas.

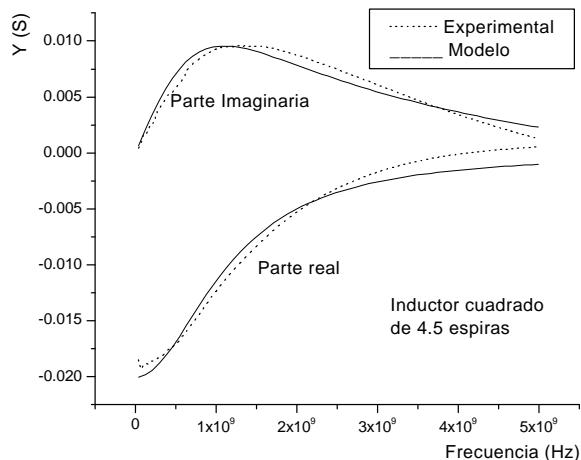

Figura 7a. Comparación modelo-experimento para el inductor de cuatro lados y 4.5 espiras.

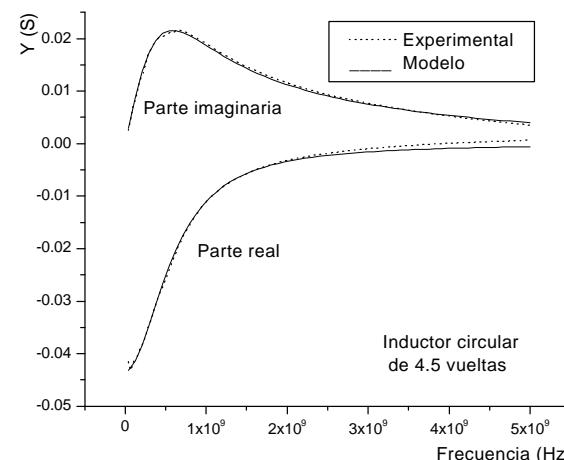

Figura 7b. Comparación modelo-experimento para el inductor circular de 4.5 vueltas.

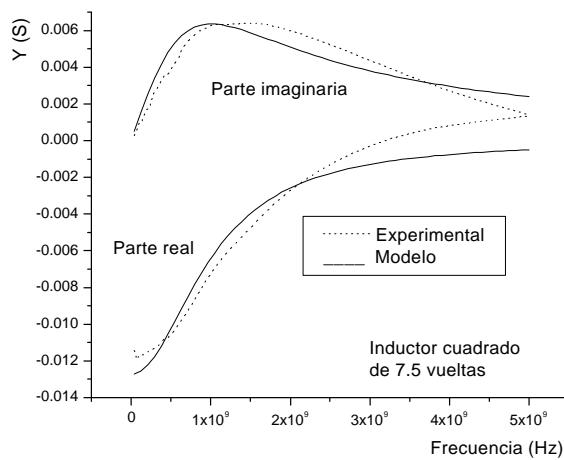

Figura 7c. Comparación modelo-experimento para el inductor de cuatro lados y 7.5 espiras.

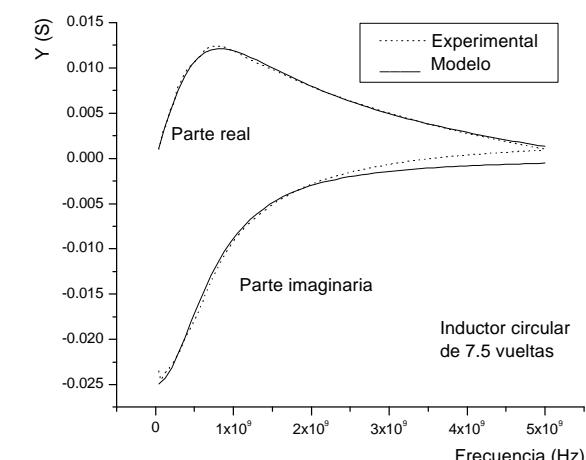

Figura 7d. Comparación modelo-experimento para el inductor circular de 7.5 vueltas.

**Tabla 1.** Resultados de la extracción de parámetros para inductores de 4.5 vueltas. El número de lados se indica en la cabeza de cada columna, siendo “Cir” el inductor circular.

| Estructura      | 4-L   | 8-L    | 10-L   | 12-L   | Cir    |

|-----------------|-------|--------|--------|--------|--------|

| <b>L</b> (nH)   | 6.86  | 4.98   | 6.28   | 3.23   | 6.29   |

| <b>R</b> (ohm)  | 49.88 | 20.31  | 40.11  | 19.93  | 23.09  |

| <b>C</b> (fF)   | 67.28 | 61.29  | 6.78   | 213    | 31.88  |

| <b>R1</b> (ohm) | 59.95 | 68.46  | 68.38  | 86.72  | 84.13  |

| <b>R2</b> (ohm) | 97.2  | 100.52 | 109.09 | 185.15 | 81.88  |

| <b>C1</b> (fF)  | 236   | 235    | 216.8  | 329    | 212    |

| <b>C2</b> (fF)  | 223   | 177    | 232.5  | 237.8  | 242.73 |

| <b>fr</b> (GHz) | 2     | 2      | 2.2    | 1.76   | 1.81   |

| <b>Q</b>        | 0.91  | 1.82   | 1.34   | 1.14   | 2.00   |

resistencia estática. Todas las mediciones se hicieron con un Analizador de Parámetros de Semiconductores (SPA) HP-4156A. Las estructuras funcionales se midieron en el rango de 40MHz a 5GHz usando un Analizador de Redes Vectorial Wiltton Modelo B. Los datos fueron desincrustados siguiendo la técnica detallada en [15]. Los datos fueron transformados a Parámetros S, y los valores de resistencias, capacitancia e inductancia obtenidos de las curvas experimentales por optimización [16]. Los datos experimentales se confrontaron para cada inductor con la respuesta predicha por el modelo eléctrico. En las Figuras 7a-7d se muestra el resultado para los inductores cuadrados y los circulares de 4.5 y 7.5 espiras. Para el inductor cuadrado, la correspondencia es adecuada, pero mejora conforme aumenta el número de lados, hasta llegar al inductor circular. De estas gráficas también se observa que el modelo representa los datos de los inductores de 4.5 espiras mejor que los de los de 7.5. Los valores promedios de los parámetros del modelo se resumen en las Tablas 1 y 2, siendo la primera para inductores de 4.5 espiras y la segunda para aquellos de 7.5 vueltas.

## 5. Conclusiones

El modelo eléctrico equivalente usado para los inductores, a pesar de ser sencillo, representa los datos experimentales satisfactoriamente. La correspondencia aumenta conforme el número de lados de los inductores, siendo mejor para los inductores circulares. Esto se atribuye al ángulo de las esquinas; mientras más agudo sea éste, mayor radiación será emitida por el inductor, constituyendo esto una pérdida

de potencia [17], no considerada en el modelo eléctrico. La correspondencia del modelo es también mejor para los inductores de 4.5 vueltas. Esto se puede explicar por la auto-inducción de corrientes en el inductor: la magnitud de esta corriente inducida es mayor mientras menor sea el radio de curvatura de la vuelta, y al eliminar las vueltas interiores se reduce este efecto.

Los resultados demuestran que la fabricación y modelado de inductores integrados es factible usando un proceso CMOS típico. Como trabajo a futuro, el modelo se debe expandir para considerar efectos de segundo orden, como son las pérdidas de potencia por los diversos mecanismos aquí detallados. En base a un modelo más completo, y a la exhaustiva caracterización de las estructuras fabricadas, se puede lograr un diseño optimizado tanto en funcionamiento como en área.

Usando procesos de fabricación maduros y robustos, como el usado aquí, se confía en la repetibilidad en la fabricación de los inductores.

## Agradecimientos

Jesús Huerta le agradece al CONACyT el apoyo otorgado a través de la Beca para Estudios de Maestría # 143926. Otro autor (RM) le agradece al CONACyT el apoyo parcial a este trabajo a través del Proyecto 33810-A. Todos los autores le agradecen a los técnicos del Laboratorio de Microelectrónica, así como a la Lic. Claudia Juárez de la Coordinación de Electrónica, por su valiosa participación

**Tabla 2.** Resultados de la extracción de parámetros para inductores de 7.5 vueltas. El número de lados se indica en la cabeza de cada columna, siendo “Cir” el inductor circular.

| Estructura      | 4-L   | 6-L   | 8-L   | 10-L  | Cir   |

|-----------------|-------|-------|-------|-------|-------|

| <b>L</b> (nH)   | 12.39 | 10.09 | 9.34  | 9.33  | 8.61  |

| <b>R</b> (ohm)  | 78.47 | 56.20 | 38.42 | 40.63 | 40.03 |

| <b>C</b> (fF)   | 2.19  | 10.03 | 2.89  | 49.13 | 60.22 |

| <b>R1</b> (ohm) | 95    | 96    | 83    | 92    | 87    |

| <b>R2</b> (ohm) | 150   | 97.45 | 89.65 | 74.11 | 62.23 |

| <b>C1</b> (fF)  | 252   | 224   | 254   | 253   | 270   |

| <b>C2</b> (fF)  | 218   | 301   | 294   | 275   | 306   |

| <b>fr</b> (GHz) | 1.57  | 1.7   | 1.52  | 1.51  | 1.52  |

| <b>Q</b>        | 0.75  | 1.11  | 1.51  | 1.36  | 1.27  |

en el desarrollo de este trabajo. También se le agradece al Dr. Celso Gutiérrez Martínez, encargado del Laboratorio de Microondas, por las facilidades prestadas en la mediciones.

## Referencias

- [1] N.M. Nguyen, R.G. Meyer, IEEE J. SSC, **25**, 1028, (1990).

- [2] J.N. Burghartz, K.A. Jenkins, M. Soyuer, IEEE EDL, **17**, 428, (1996).

- [3] Pieters, E. Beyne, Proc. Int. Conference on Multichip Modules and High Density Packaging, 478, (1998).

- [4] F. Mernyei, F. Darrer, A. Sibrai, IEEE Microwave and Guided Wave Letters, **8**, 300, (1998)

- [5] K.B. Ashby, I.A. Koullias, W.C. Finley, J.J. Bastek, S. Moinian, IEEE J. SSC, **31**, 4, (1996).

- [6] C.P. Yue, S.S. Wong, IEEE Trans. on Electron Devices, **47**, 560, (2000).

- [7] J.R. Long, M.A. Copeland, IEEE J. SSC, **32**, 357, (1997).

- [8] J.N. Burghartz, D.C. Edelstein, M. Soyuer, H. A. Ainspan, K.A. Jenkins, IEEE J. SSC, **33**, 2028, (1998).

- [9] J.Kim, J. Koeppe, M. Hsieh, R. Harjani, Proc. Midwest Symposium on Circuits and Systems, 790, (2000).

- [10] Y.Koutsoyannopoulos, Y.Papananos, S. Bantas, C Alemanni, Proc. ISSCAS, (2000).

- [11] Y. Koutsoyannopoulos, Y. Papananos , C. Alemanni, S. Bantas , Proc. ESSIRC, 320, (1997).

- [12] A.M. Niknejad, R.G. Meyer, J.L. Tham, Proc. ESSCIRC, 198, (1999).

- [13] T.H. Lee, "The Design of CMOS Radio-Frequency Integrated Circuits", Cambridge University Press, Cambridge, EUA, (1998).

- [14] R. Murphy, "Teoría Electromagnética", Editorial Trillas, México, (2001).

- [15] R. Murphy, "Prospects for the MOS Transistor as a High-Frequency Device", Tesis Doctoral, INAOE, México, (1997).

- [16] R. Murphy, Revista Imaquinación, INAOE, **1**, 12, (1998).

- [17] C.A. Balanis, "Antenna Theory, Analysis and Design", John Wiley & Sons, Nueva York, EUA (1997).