Ingeniería, investigación y tecnología

ISSN: 1405-7743

Facultad de Ingeniería, UNAM

Medina-Vázquez, Agustín Santiago; Flores-Castillo, Pablo David;

Bonilla-Barragán, Carlos Alberto; Gurrola-Navarro, Marco Antonio;

Meda-Campana, María Elena; Villegas-González, José Martín

Metodología de bajo costo para implementar circuitos electrónicos integrados, un ejemplo de aplicación

Ingeniería, investigación y tecnología, vol. XX, núm. 3, e029, 2019, Julio-Septiembre

Facultad de Ingeniería, UNAM

DOI: <https://doi.org/10.22201/fi.25940732e.2019.20n3.029>

Disponible en: <https://www.redalyc.org/articulo.oa?id=40465052005>

- Cómo citar el artículo

- Número completo

- Más información del artículo

- Página de la revista en [redalyc.org](https://www.redalyc.org)

## Metodología de bajo costo para implementar circuitos electrónicos integrados, un ejemplo de aplicación

## A low-cost methodology for implementing electronics integrated circuit, an application example

Medina-Vázquez Agustín Santiago

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara

Correo: [santiago.medina@ceei.udg.mx](mailto:santiago.medina@ceei.udg.mx)

<https://orcid.org/0000-0002-3562-2921>

Flores-Castillo Pablo David

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara

Correo: [pablo.flores@alumnos.udg.mx](mailto:pablo.flores@alumnos.udg.mx)

<https://orcid.org/0000-0003-3059-6231>

Bonilla-Barragán Carlos Alberto

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara

Correo: [cbonilla\\_esc@yahoo.com.mx](mailto:cbonilla_esc@yahoo.com.mx)

<https://orcid.org/0000-0003-4803-8422>

Gurrola-Navarro Marco Antonio

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara

Correo: [marco.gurrola@ceei.udg.mx](mailto:marco.gurrola@ceei.udg.mx)

<https://orcid.org/0000-0001-8446-7764>

Meda-Campana María Elena

Centro Universitario de Ciencias Económico Administrativas

Universidad de Guadalajara

Correo: [mmeda.campana@gmail.com](mailto:mmeda.campana@gmail.com)

<https://orcid.org/0000-0001-8684-8296>

Villegas-González José Martín

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara

Correo: [jose.villegas.jv8@gmail.com](mailto:jose.villegas.jv8@gmail.com)

<https://orcid.org/0000-0002-3091-2065>

### Resumen

En la industria nacional mexicana se importan grandes cantidades de dispositivos electrónicos para las empresas de manufactura, entre los que se encuentran los circuitos integrados. Dado que estos circuitos integrados son diseñados en otros países, en México se pierden oportunidades de participación en el sector. En este documento, se presenta una metodología para diseñar circuitos integrados con herramientas de bajo costo con el fin de impulsar el interés en el área, aún con recursos económicos limitados, dejando la implementación de los mismos a empresas dedicadas. Como caso de éxito, se muestra el diseño de un circuito correlador de tramas de bits en una tecnología de fabricación CMOS. El correlador se diseñó para proporcionar salida digital y salida analógica (circuito de señal mezclada). Se sigue un modelo de desarrollo del chip conocido como "fabless" (sin fábrica) y los prototipos obtenidos fueron probados con éxito en el laboratorio. A pesar de que los resultados obtenidos en laboratorio aun no alcanzan la eficiencia de los circuitos comerciales, los circuitos que aquí se muestran son suficientes para validar la metodología discutida y la cual está al alcance de emprendedores y estudiantes para incursionar en el ramo del diseño de circuitos integrados.

**Descriptores:** Circuitos integrados, México, América Latina, diseño, bajo costo, fabless, academia, correlador.

### Abstract

In the Mexican national industry, large quantities of electronic devices are imported for manufacturing companies, including integrated circuits. Since these devices are designed in other countries, opportunities for participation in the industrial sector are lost in Mexico. In this document, a methodology is presented to design integrated circuits with low-cost tools in order to promote interest in the area, even with limited economic resources. As a case of success, it shows the design of a correlator circuit in a CMOS manufacturing technology. The correlator was designed to provide a digital output and an analogue output (mixed signal circuit). In this work, a chip development model known as "fabless" (without factory) is followed and the obtained prototypes were successfully tested in the laboratory.

**Keywords:** Integrated circuits, Mexico, Latin America, design, low-cost, fabless, academy, correlator.

## INTRODUCCIÓN

En este trabajo se muestra una metodología de diseño de circuitos integrados digitales y analógicos que permite la reducción en costos. A continuación, se muestra un marco teórico para posteriormente pasar a la descripción del método.

### LA INDUSTRIA DE LA ELECTRÓNICA EN MÉXICO

La industria de la electrónica en el mundo, ha mostrado un crecimiento exponencial desde la aparición de los primeros dispositivos semiconductores a mediados del siglo XX. La aparición del concepto de Circuito Integrado (CI) en la década de los 1950's contribuyó de manera decisiva a la generación de la tecnológica como ahora la conocemos. Un CI es un dispositivo de pequeñas dimensiones (algunos milímetros cuadrados) que contiene transistores, diodos, resistencias, capacitores, y otros elementos electrónicos sobre una superficie de silicio (sustrato) y que realizan el procesamiento de señales eléctricas para cumplir con una función de utilidad. Hoy en día, esta tecnología se encuentra en constante evolución, demandando desorbitantes cantidades de recursos humanos y económicos (Martínez *et al.*, 2016; Hoeren, 2016).

Particularmente, la participación de México en la industria global de la electrónica es por medio de la manufactura de aparatos. México es un país que por medio de acuerdos gubernamentales con empresas transnacionales ha generado un ecosistema que ofrece mano de obra para la manufactura de aparatos electrónicos como televisores, teléfonos celulares, dispositivos de red, entre otros.

Por otro lado, PROMEXICO es un organismo que pertenece al Estado Mexicano y que se encarga de fortalecer las relaciones entre México y otros países, en cuanto a exportaciones e importaciones se refiere. En su informe del año 2015 (PROMEXICO, 2015), señala que en el año 2014 la industria electrónica en todo el planeta tuvo una producción equivalente a los 3,798 miles de millones de dólares (mmd) y particularmente en México de 80,125 millones de dólares (mdd) en exportaciones y 85,217 mdd en importaciones. El reporte aclara que, de la producción mundial, 15% se debe a la participación de América del Norte, en donde está incluido México. En contraste, El resto de América Latina tuvo, en 2014, una participación de 1% en la industria. Como dato interesante, se prevé en México un crecimiento en la producción con una Tasa Media de Crecimiento Anual (TMCA) de 3.2% y un consumo con una TMCA de 4.5% en el intervalo del 2014 al 2020.

Sin embargo, los CIs que se utilizan en las empresas de ensamblado y manufactura en el mundo para el armado de los sistemas electrónicos son casi en su totalidad material de importación. Por ejemplo, se estima que en 2013 un 97% de los componentes necesarios para la fabricación de televisores fueron de origen extranjero y que los componentes electrónicos activos (diodos, displays, transistores, CIs) significaron montos de importación de más de 3 mil millones de dólares. Estos dispositivos vienen de Corea del Sur, Malasia y Estados Unidos y algunos otros países en muy menor medida.

En general, las empresas relacionadas con la producción de dispositivos electrónicos se clasifican en EMS (Electronics Manufacturing Services), las cuales se dedican solamente a la manufactura por encargo de otras empresas, OEM (Original Equipment Manufacturing), que manufacturan productos de su propia firma, pero que se usan en sistemas más complejos diseñados por terceros y (ODM, Original Design Manufacturer), las cuales además de hacer la manufactura de sus productos, ellos mismos los utilizan en sus propios sistemas (PROMEXICO, 2015). Así, México es un país que cuenta con una gran cantidad de empresas de manufactura EMS, un número muy reducido de empresas OEM y un número aún menor de empresas ODM.

### EMPRESAS SIN FUNDIDORAS (FABLESS)

Una empresa que diseña CIs no necesariamente debe tener su propia fundidora. Una fundidora es la que se encarga de construir los circuitos integrados sobre una oblea de silicio u otro tipo de sustrato. Diseñar un CI y construirlo son dos procesos completamente distintos (aunque relacionados) y cada uno requiere de un tipo de especialización particular, por lo que pueden llevarse a cabo por diversas entidades en diferentes partes del mundo. En los modelos de negocios, es posible hablar de empresas IDM (Integrated Device Manufacturer) y Fabless (Sin fábrica). Las IDMs tienen capacidad para producir circuitos integrados incluyendo el diseño, la fabricación, pruebas, ensamblaje, empaquetado y márguetin. Empresas con este modelo son Intel, IBM y Texas Instruments (Sarma & Li, 2016).

Actualmente, la mayoría de las empresas fabless se encuentran en América del Norte, mientras que las fundidoras se establecieron en la región de Asia Pacífico. Ejemplos de empresas sin fábrica son Qualcomm, Broadcom, Advanced Micro Devices (AMD) y MediaTek. Por otro lado, como ejemplos de fundidoras se tiene a The MOSIS Service (Estrictamente hablando, The MOSIS Service (<https://www.mosis.com/>), empresa del Information Sciences Institute de la Universidad del

Sur de California, es un intermediario entre las grandes maquiladoras de CIIs con aquellos interesados en realizar prototipado o producción de bajo volumen, académicos o industriales). Taiwan Semiconductors Manufacturing Company, United Microelectronics Corporation y Semiconductor Manufacturing International Corporation. La gran ventaja que ofrece el modelo “fabless” es que, debido a que se enfoca más en la etapa de diseño que en las de fabricación, se tienen tiempos más cortos para madurar una tecnología de interés. Como ejemplo del éxito de este modelo se puede decir que en 2015 la empresa Qualcomm vendió 16,032 mdd y MediaTek vendió 6,504 mdd (Sarma & Li, 2016).

Por lo anterior, lo que se propone es que en México se haga el diseño de circuitos integrados utilizando las herramientas de software y dedicar tiempo y esfuerzo a esta actividad. Posteriormente, mandar a fabricar los circuitos en silicio a una fundidora sin la preocupación de los enormes gastos y esfuerzos que requiere la operación de la fundidora.

### EL SOFTWARE EDA

El software EDA (Electronic Design Automation) son programas de simulación de muy alto grado de precisión para el diseño de circuitos electrónicos tanto integrados como de placa impresa. Con este tipo de software, es posible obtener resultados de simulación similares a los que se van a medir en el laboratorio cuando el CI sea fabricado. El software EDA más popular para el diseño de circuitos eléctricos, en general, es el SPICE (Simulation Program with Integrated Circuits Emphasis) desarrollado desde la década de 1970 en California, Estados Unidos. Al combinar este software con un modelo avanzado de parámetros del transistor MOSFET, es posible diseñar circuitos electrónicos para su integración desde un ambiente de simulación. Un modelo ampliamente aceptado para la descripción funcional de los transistores MOSFET es el modelo BSIM (Liu & Hu, 2011). A pesar de que existen versiones de SPICE con licencias costosas (algunas decenas de miles de dólares anuales) también existen versiones libres o gratuitas de SPICE, las cuales se pueden encontrar en Internet, como por ejemplo, LTspice (<http://www.linear.com/design-tools/software/>) (Brocard, 2013). Este software permite simular circuitos analógicos y digitales a nivel transistor y se encuentra con licencia gratuita (Freeware) en su página oficial.

Por otro lado, una herramienta ampliamente recomendable y de licencia libre para el diseño de CIIs digitales de muy alto grado de integración (millones de transistores) es Alliance CAD System (<https://soc-extras.lip6.fr/en/alliance-abstract-en/>).

Alliance es un conjunto de herramientas CAD (Computer Aided Design) de licencia libre y de librerías portables para el diseño de circuitos integrados digitales VLSI. Este incluye un compilador VHDL y un simulador, así como herramientas de síntesis (transformación de descripciones en lenguaje VHDL a celdas electrónicas interconectadas) y una herramienta para la colocación de celdas y el ruteo de pistas de metal (interconexiones entre celdas). Dado que está dirigido al diseño con transistores MOSFET, cuenta con una librería para la tecnología CMOS (Complementary MOSFET). Alliance es desarrollado por el laboratorio LIP6 de la Universidad Pierre & Marie Curie University de París, Francia. Este software ha sido utilizado incluso para el diseño de microprocesadores de muy alta densidad ( $> 400,000$  transistores). Se permite el uso de este software incluso para diseños comerciales sin pagar ningún tipo de regalía para la Universidad creadora. Su uso se realiza en sistemas operativos basados en Linux. Adicionalmente, en su página oficial es posible acceder a los manuales de uso del software.

### LA ACADEMIA MEXICANA Y LOS CIRCUITOS INTEGRADOS

Según datos de la Secretaría de Educación Pública (SEP) de México, existen más de cien universidades y centros tecnológicos que imparten carreras afines a la ingeniería en electrónica. Sin embargo, solo un muy reducido número de ellas incluyen el diseño de circuitos integrados dentro de sus programas. Por lo general, estos temas quedan pospuestos para estudios de posgrado y solo instituciones como el Instituto Nacional de Astrofísica, Óptica y Electrónica (INAOE), Centro de Investigación y de Estudios Avanzados (CINVESTAV), Instituto Politécnico Nacional (IPN), Universidad Nacional Autónoma de México (UNAM), y el Instituto Tecnológico y de Estudios Superiores de Occidente (ITESO), ofrecen la alternativa. Algunas instituciones ya han iniciado su incursión en este campo, tal es el caso de la Benemérita Universidad Autónoma de Puebla (BUAP), el CUCEI (Centro Universitario de Ciencias Exactas e Ingenierías ([www.depel.cucei.udg.mx/](http://www.depel.cucei.udg.mx/))) de la de Guadalajara, y el Centro de Ingeniería y Desarrollo Industrial (CIDEI), entre otras.

Es un hecho que los programas de la carrera de ingeniero en electrónica (y algunas carreras afines) proporcionan los conocimientos necesarios para que el estudiante emigre de manera relativamente directa hacia el diseño de CIIs. Cabe mencionar que las estrategias para diseñar CIIs difiere levemente del diseño de circuitos con elementos discretos (Sedra & Smith, 2014). Los

programas de licenciatura incluyen la enseñanza de técnicas de diseño electrónico digital y analógico, además de cubrir temas relacionados a la teoría de semiconductores. Sin embargo, se presenta una carencia en temas relacionados al uso del transistor MOSFET en circuitos. Cabe mencionar que, en las tecnologías basadas en silicio, el transistor MOSFET es el imperante. Es por eso que resulta altamente recomendable hacer énfasis en la enseñanza de la tecnología de MOSFET complementario (CMOS) desde los programas de licenciatura.

Para la mayoría de las actividades relacionadas con el diseño de CI's se requiere del uso de software CAD. Sin embargo, es de vital importancia que el diseñador conozca las técnicas de diseño digital, arquitectura de procesadores, electrónica analógica y afines. Los cursos en la academia deben incluir el análisis de la señal eléctrica desde su generación, su procesamiento, susceptibilidad al ruido, interferencias electromagnéticas, variaciones de parámetros y demás problemas afines.

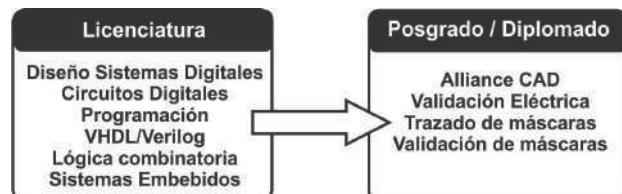

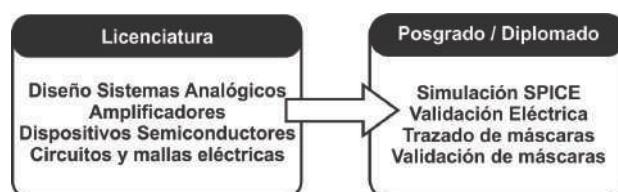

La Figura 1 muestra las materias más importantes para que un estudiante de posgrado egrese con los conocimientos necesarios para el diseño de CI's digitales. De manera similar, la Figura 2 muestra las materias más importantes para que el alumno egrese de la maestría con la capacidad de diseñar CI's de procesamiento analógico. Al combinar ambos conocimientos, el alumno egresará con la capacidad de diseñar CI's de procesamiento de señal mezclada.

En este documento se discute la metodología para generar CI's desde su concepción hasta las pruebas experimentales mostrando un caso de éxito. Debido a que en este proyecto no se contó con una fundidora, se siguió un modelo fabless, es decir, el artículo se centró en el diseño y se dejó de lado el caso de la fundidora a The MOSIS Service. Por motivos de espacio, el presente trabajo no pretende ser un tutorial detallado sino una descripción concisa, sin embargo, se proporcionan fuentes bibliográficas complementarias. Para ello, se presenta como ejemplo el diseño de un circuito correlador de dos secuencias de bits con salida digital y salida analógica (circuito de señal mezclada). Se debe mencionar que la metodología aquí discutida es similar a la aplicable

Figura 1. Bosquejo de plan académico propuesto para diseñar sistemas digitales integrados

en el diseño de otro tipo de CI's, como algunos tipos de sensores y memorias.

El método inicia al tener claras las definiciones correctas de lo que se va a implementar, es decir, tener de manera completamente clara qué función deseamos que realice el circuito. Esto nos permite trazar una estrategia de implementación basándonos en los conocimientos adquiridos en la academia.

Una vez que se cuenta con diagramas de bloque, diagramas de flujo, pseudocódigos, etcétera, se procede a la síntesis de la idea conceptual construyendo un código VHDL. Las herramientas de Alliance CAD System permiten desarrollar flujos de diseño a partir de la descripción del sistema en lenguaje de descripción de hardware VHDL. Alliance cuenta con herramientas para manejar tanto descripciones en VHDL comportamental, donde la descripción del circuito se hace indicando las funciones de alto nivel que va a realizar, como en VHDL estructural, lista de celdas que conforman el circuito y de sus interconexiones (Maxinez, 2013). El proceso de síntesis esencialmente consiste en convertir una descripción en VHDL comportamental a una descripción estructural. Sobre esta última descripción se puede aplicar la metodología de posicionado y ruteado (P&R) para generar los planos de fabricación.

Para probar la viabilidad de todo lo expuesto anteriormente, en las siguientes secciones se muestra la estrategia seguida para el diseño y la implementación de un correlador de secuencias de bits.

## DESARROLLO

DEFINICIONES Y ESTRATEGIA. EL CORRELADOR DE BITS Y UNA ARQUITECTURA PROPUESTA

### DESCRIPCIÓN DEL PROBLEMA

Un correlador de bits es un circuito de procesamiento de señales binarias que realiza la operación de correlación  $r_{xy}(m)$  dada por la ecuación

$$r_{xy}(m) = \sum_{n=1}^k x(n)y(n-m)$$

Figura 2. Bosquejo de plan académico propuesto para diseñar sistemas analógicos integrados

Donde  $x(n)$  es una secuencia causal y finita de  $k$  elementos, donde  $m = \{0, 1, 2, \dots\}$  son los desplazamientos relativos entre las dos secuencias  $x(n)$  e  $y(n)$ . En el caso  $x(n) = y(n)$  se habla de una autocorrelación. Por lo general, una de las secuencias se mantiene fija mientras que la otra secuencia se desplaza  $m$  posiciones desde su posición inicial. Por cada desplazamiento, el producto bit a bit de las secuencias resultantes debe realizarse para luego obtener la suma de los productos obtenidos individualmente. La correlación es una operación útil para obtener el grado de similitud entre dos secuencias. En el desplazamiento  $m$  para el cual las secuencias tengan mayor similitud, la suma de productos, y por ende la correlación, será mayor.

#### ESTRATEGIA DE DISEÑO

Dadas las necesidades discutidas previamente, se genera una estrategia de diseño de un sistema que realice la correlación de dos secuencias de bits. La estrategia se describe a continuación.

Para diseñar el correlador de  $n$  bits, se propone crear un registro de corrimiento de carga serial activado con una señal externa para cargar la primera secuencia, a decir  $x(n)$ . Al llenarse este registro con la secuencia deseada, esta debe trasladarse a otro registro de carga paralela por medio de una señal externa que active la carga. Posteriormente, se carga la siguiente secuencia, es decir,  $y(n)$ , al registro de corrimiento y esta secuencia se desplaza una posición ( $n-m$ ) cada que una señal externa de corrimiento se active. En cada desplazamiento se realiza la suma de productos correspondiente. Así, las salidas de estos dos registros deberán entrar a un sub-modulo compuesto de compuertas AND para generar el produc-

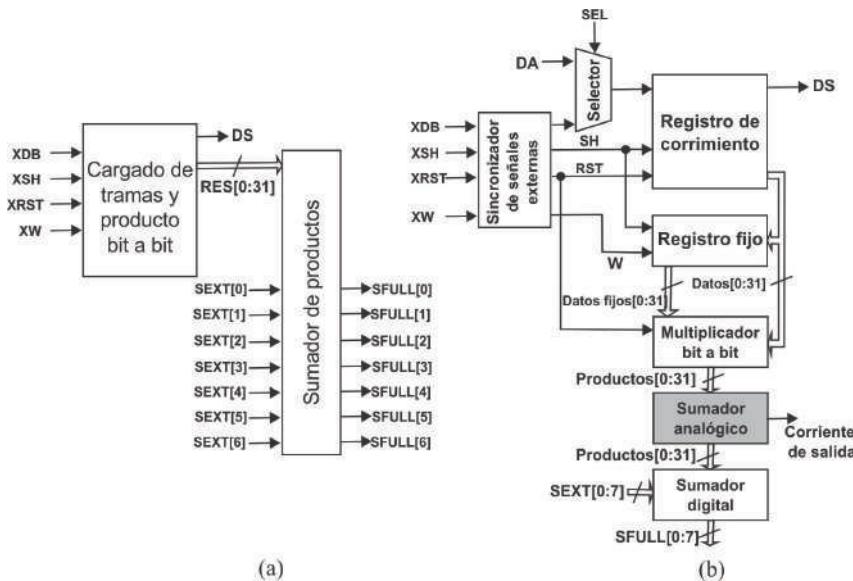

to bit a bit de las secuencias contenidas en el registro y finalmente se requerirá de un sumador para obtener el resultado final (Flores, 2013). La arquitectura descrita anteriormente se presenta en la Figura 3. La Figura 3a muestra la arquitectura de alto nivel del correlador enteramente digital y la Figura 3b muestra la arquitectura de manera detallada, incluyendo un sumador analógico en la etapa de salida. Note que esta arquitectura incluye las dos versiones del correlador. En un caso se obtendrá la salida en formato digital (sumador digital) y en el otro se obtendrá la salida en formato analógico (sumador analógico). La Tabla 1 describe el significado de cada abreviatura de las señales utilizadas.

Se debe aclarar que, en este caso, para realizar las pruebas de laboratorio, el sistema se diseña para que la secuencia que se desplaza,  $y(n)$ , se retroalimente al mismo registro y tener así un efecto de correlación cíclica y se facilite la observación en el osciloscopio.

#### SÍNTESIS Y VERIFICACIÓN DEL SISTEMA

Después de definir la arquitectura, se pasa al proceso de síntesis. Esto se logra utilizando la herramienta de Alliance. Para ampliar conocimientos sobre Alliance, se recomienda ver los libros o manuales proporcionados por el laboratorio LIP6 de la Universidad Pierre & Marie Curie University de París en su sitio web oficial, como por ejemplo (Silva *et al.*, 2006).

El flujo de síntesis parte de una descripción de hardware en VHDL comportamental, con el cual se obtendrá un archivo estructural, es decir, un archivo que representa las celdas y compuertas digitales, las cuales se toman de una librería previamente proporcionada

Figura 3. a) Arquitectura para el correlador para una salida digital y b) arquitectura detallada que incluye salida en formato digital y analógico

Tabla 1. Descripción de las señales utilizadas en la arquitectura del correlador

| Señal    | Descripción                                                                                                                         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| XDB      | Entrada serial de bits                                                                                                              |

| XSH      | Shift. Desplaza los bits uno a uno, en flanco de subida                                                                             |

| XRST     | Reset. Borra los registros, en flanco de subida                                                                                     |

| XW       | External write. Escribe en registro fijo, con el flanco de subida                                                                   |

| SEXT[i]  | Suma externa. Sirve para conectar otro circuito integrado y aumentar el tamaño de las secuencias procesadas                         |

| SFULL[i] | Bus de resultado de la suma completa. Es la suma de los datos ingresados por DB más la externa                                      |

| DA       | Por esta entrada ingresan los datos cuando se hace autocorrelación, se conecta con la salida DS                                     |

| DS       | Salida de los datos de forma serial para hacer autocorrelación                                                                      |

| SEL      | Se pone en estado alto para hacer autocorrelación                                                                                   |

| SH       | Señal que se usa para desplazar los bits                                                                                            |

| W        | Señal que se usa para escribir en el registro fijo                                                                                  |

| RES[i]   | Es el resultado del producto bit a bit (lo que sale de las operaciones AND de la secuencia del registro fijo con el de corrimiento) |

por Alliance, llamada SXLIB. La estructura del sistema puede construirse de manera automática o puede utilizarse la herramienta GENLIB para construir la estructura de forma manual. Cabe mencionar que este flujo de síntesis digital con Alliance se trata a mayor profundidad en (Chávez *et al.*, 2015).

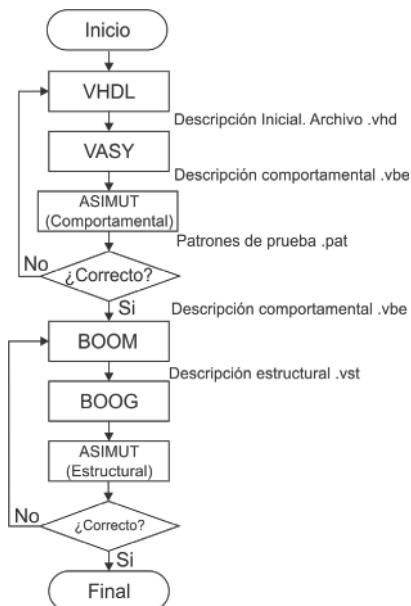

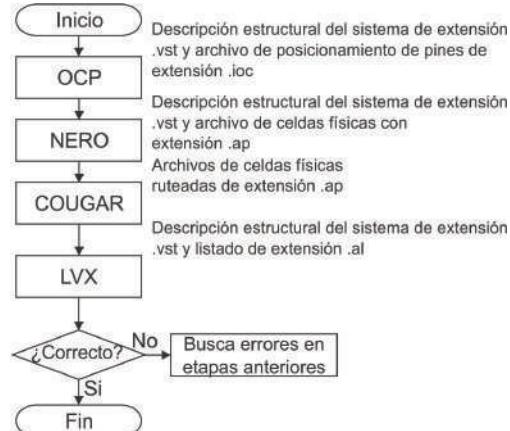

En la Figura 4 se muestra un flujo de diseño convencional que sigue la herramienta de Alliance para generar un archivo en VHDL estructural a partir de la descripción desarrollada en lenguaje VHDL comportamental.

La descripción en VHDL es un archivo que debe ser procesado por la herramienta VASY que interpreta su contenido y la transforma en una descripción más simple, adecuada para las siguientes herramientas de Alliance. Paso seguido, se lleva a cabo una verificación comportamental con la herramienta de simulación ASIMUT, es decir, se verifica que el sistema realice las funciones deseadas comprobándolo con ayuda de un archivo de patrones de prueba. Después de la verificación comportamental, se utiliza la herramienta BOOM, la cual intenta simplificar las expresiones booleanas complejas. La herramienta BOOG se encarga de obtener una representación del sistema en VHDL estructural. Para ello, emplea únicamente celdas de la librería SXLIB. Por último, se realiza una nueva verificación de la descripción estructural con la herramienta ASIMUT.

Como puede verse, todo este proceso se realiza en una computadora con el software de licencia libre, lo que lo hace un proceso que demanda muchas horas de planeación y trabajo, pero que resulta de muy bajo costo en cuanto a recursos materiales se refiere.

#### POSICIONAMIENTO Y RUTEO (P&R)

Continuando con el proceso para generar un CI, es necesario realizar el posicionamiento de las celdas acotándose al área de silicio disponible. Una celda puede ser una compuerta lógica, un multiplexor, un sumador o cualquier otra de las 94 celdas disponibles en la librería SXLIB.

El diagrama de flujo del posicionamiento y ruteo de los bloques que conforman el sistema se muestra en la Figura 5. La herramienta OCP realiza el posicionamiento de los componentes del sistema obtenidos en la descripción estructural del sistema creado en el proceso de la Figura 4. Después, la herramienta NERO se encarga de realizar la interconexión de las celdas, con base en la información contenida en la descripción en VHDL estructural del sistema.

En este punto, después de la aplicación de las herramientas OCP y NERO ya se cuenta con un plano de fabricación. Para verificar que el plano no contiene errores introducidos por alguna de estas herramientas, la herramienta COUGAR extrae un nuevo listado estructural a partir del plano. La herramienta LVX se encarga de la comparación de los archivos estructurales producidos de manera independiente por BOOG (Figura 4.) y por NERO (Figura 5). Cabe mencionar que en cualquier etapa se pueden generar errores en la representación del sistema debidos a fallas humanas o a bugs de los programas. Si estos se detectan, se deberá volver a las etapas anteriores para buscar corregirlos.

Figura 4. Diagrama de flujo del flujo de síntesis

#### DEFINICIONES ESTRUCTURALES MANUALES

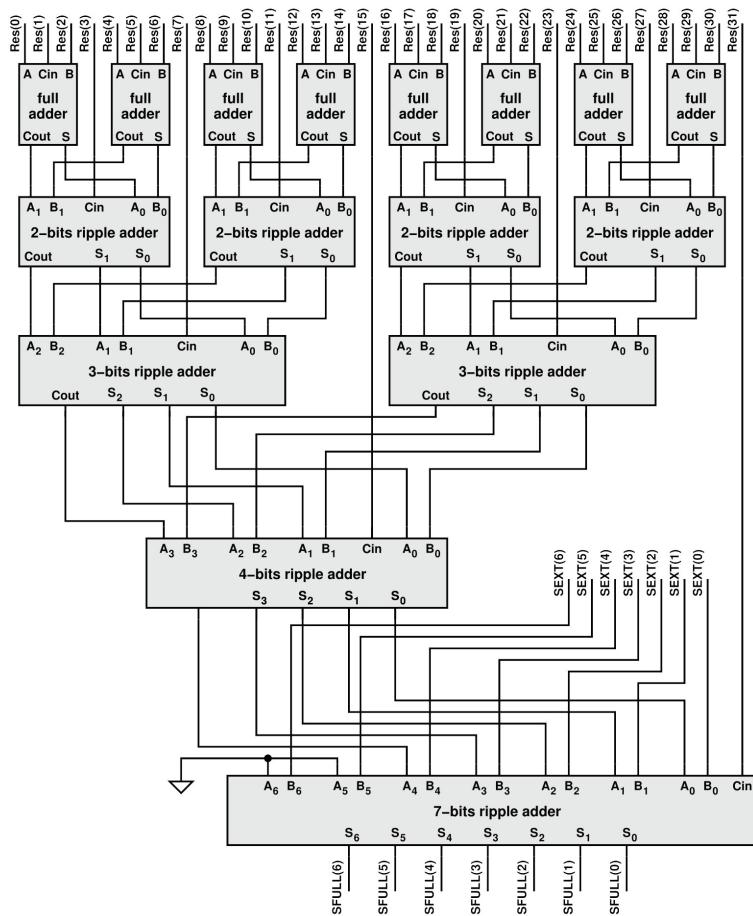

No siempre es conveniente definir la arquitectura de un bloque digital de manera comportamental, sino que se puede recurrir a la definición de las estructuras de forma manual. Un ejemplo de ello es el sumador de productos de la Figura 3a cuya arquitectura optimizada para bajo consumo de área de silicio se muestra en el diagrama esquemático de la Figura 6. Este módulo realiza la suma simultánea de 32 sumandos de 1 bit.

El bloque se desarrolló mediante un flujo de diseño con Alliance que involucra las funciones de GENLIB. En vez de describir la arquitectura directamente en lenguaje VHDL estructural (tarea muy propensa a errores cuando se hace manualmente), se recomienda hacer la descripción en lenguaje C empleando las funciones de GENLIB.

Los 5 tipos de módulos que aparecen en la Figura 6 se componen únicamente del módulo de la celda “fulladder\_x2” o sumador completo (de la librería SXLIB). Los sumadores de riso de 2, 3, 4 y 7 bits contienen 2, 3, 4 y 7 celdas “fulladder\_x2”, respectivamente. El diseño completo del módulo requiere de 33 de estas celdas básicas en total. Una vez que la estructura se ha descrito en lenguaje C, este archivo se compila con el comando GENLIB generando el archivo correspondiente en formato VHDL estructural.

Hay que señalar que, si llamamos  $\tau$  al retardo de una celda NAND ó NOR básica, el retardo total de este módulo es de  $44\tau$  (aproximadamente). Si reemplazáramos los sumadores de riso de 3, 4 y 7 bits, por sumadores de adelanto de acarreo entonces obtendríamos un

Figura 5. Diagrama de flujo para el posicionamiento y ruteo del sistema

retardo de tan solo  $28\tau$  (aproximadamente). Esto último a expensas de mayores requerimientos de área de silicio pues este tipo de sumador, aunque más veloz, requiere mayor cantidad de circuitería interna.

#### ETAPA DE SALIDA EN FORMATO ANALÓGICO-SUMADOR DE PRODUCTOS ANALÓGICO

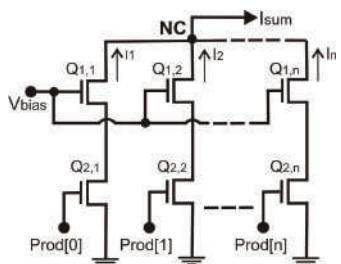

Para generar el bloque de salida analógica, se implementó un sumador en modo corriente. En este caso, la etapa de salida analógica consiste en un sumador analógico constituido por 32 arreglos de dos transistores, como se muestra en la Figura 7. Este arreglo es primariamente implementado en el simulador SPICE para la validación funcional.

La compuerta de cada uno de los MOSFETs superiores está conectada a un voltaje de polarización  $V_{bias}$  para mantenerlos saturados y la compuerta del transistor inferior se conecta a cada uno de los productos provenientes del multiplicador de productos bit a bit (Prod[0] hasta Prod[n]) de las etapas diseñadas con Alliance. De esta forma, cuando Prod[n] se pone en alto, el arreglo de transistores correspondiente se comporta como una fuente de corriente generando la corriente  $I_n$ . Cada corriente generada en cada rama se suma al nodo común NC, señalado en la Figura 7. De esta forma, se obtiene una corriente  $I_{sum}$  proporcional al nivel de correlación de las dos secuencias involucradas.

Figura 6. Sumador digital

Figura 7. Sumador en modo corriente implementado con transistores MOSFET

#### TRAZADO DE MÁSCARAS PARA LA ETAPA ANALÓGICA DE SALIDA

En el caso del sumador analógico en modo corriente, el trazado de máscaras de la parte analógica se realizó manualmente utilizando el software de licencia libre Magic (<http://opencircuitdesign.com/magic/>), que se encuentra en Internet. Magic es desarrollado por la Universidad de Berkeley desde los años 80's (Baker, 2010), pero con mejoras continuas hasta hoy en día. Debido a que se trata de un software de licencia libre, se ha utilizado por muchas universidades, centros de investi-

gación y pequeñas empresas. Su uso se realiza en sistemas operativos basados en Linux.

#### PROCESO DE FABRICACIÓN EN SILICIO

Siguiendo un modelo fabless, se procedió a enviar las máscaras a la empresa The MOSIS Service. En este caso, MOSIS proporcionó el proceso de fabricación para una tecnología CMOS de On Semiconductor de 0.5 micras. Aunque esta tecnología resulta ser relativamente grande en la actualidad, sirve para efecto de validar la metodología propuesta en este documento. Cabe mencionar que esta es una etapa que requiere de un presupuesto que comienza desde los 8'000 dólares americanos o más, según la tecnología deseada. Sin embargo, sería por mucho, más costoso mantener una fundidora.

#### PRUEBAS DE LABORATORIO

Cuando la empresa MOSIS envía el prototipo en silicio, se procede a la etapa de pruebas eléctricas. Para probar el funcionamiento del sistema, se utilizó un microcon-

trolador PIC18F4550, que fue programado para generar las señales de control del sistema y generar las secuencias de datos a correlacionar. Esto es porque las secuencias deben de ser introducidas bit a bit y, posteriormente, una de ellas debe de ser desplazada con los pulsos del reloj.

Para validar la operación de nuestro prototipo, se realizaron pruebas exhaustivas de donde se decidió reportar tres casos de pruebas diferentes:

- 1) Cuando ambas secuencias de entrada son ortogonales entre sí.

- 2) Cuando las secuencias contienen bits de distribución aleatoria, pero ambas secuencias son iguales.

- 3) Cuando ambas secuencias de distribución aleatoria son diferentes.

Las pruebas se realizaron con dos CIs interconectados en serie para validar que el sistema puede ser escalado y procesar secuencias de un mayor número de bits. Un par de prototipos, de los cinco que fabricó MOSIS, no funcionaron, probablemente por afectaciones de descargas eléctricas.

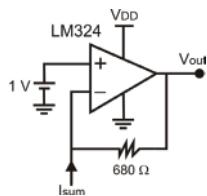

Para verificar la etapa de salida analógica fue necesario agregar un circuito externo al CI conformado por amplificadores inversores implementados con amplificadores operacionales (LM324), como el que se muestra en la Figura 8. La utilidad de este circuito es transformar la señal  $I_{sum}$  de modo corriente a modo voltaje  $V_{out}$ , lo que permite utilizar un osciloscopio como vehículo de observación. Esta etapa debe diseñarse para los requerimientos de corriente de la etapa siguiente, pero para los objetivos de este documento, esta configuración es suficiente.

La prueba de la respuesta en modo corriente (salida analógica) se realizó con una frecuencia de reloj general de 250 kHz y la de las salidas digitales con una frecuen-

Figura 8. Circuito implementado para convertir la corriente de salida a modo voltaje

cia de 25 Mhz. Cabe mencionar que el diseño analógico para señales de radiofrecuencia conlleva a consideraciones adicionales. Dado que aquí se desea discutir la metodología de diseño, consideramos que las frecuencias reportadas son aceptables para el caso.

## RESULTADOS OBTENIDOS

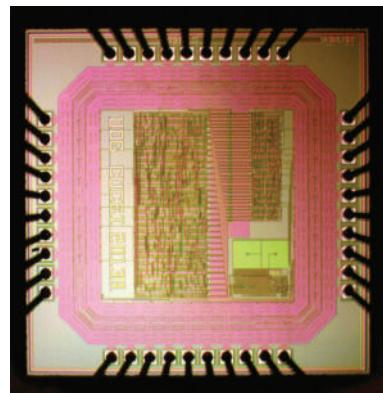

En la Figura 9 se muestra en una microfotografía del circuito integrado obtenido. Este circuito se encuentra dentro de un paquete de cuarenta patitas o pines.

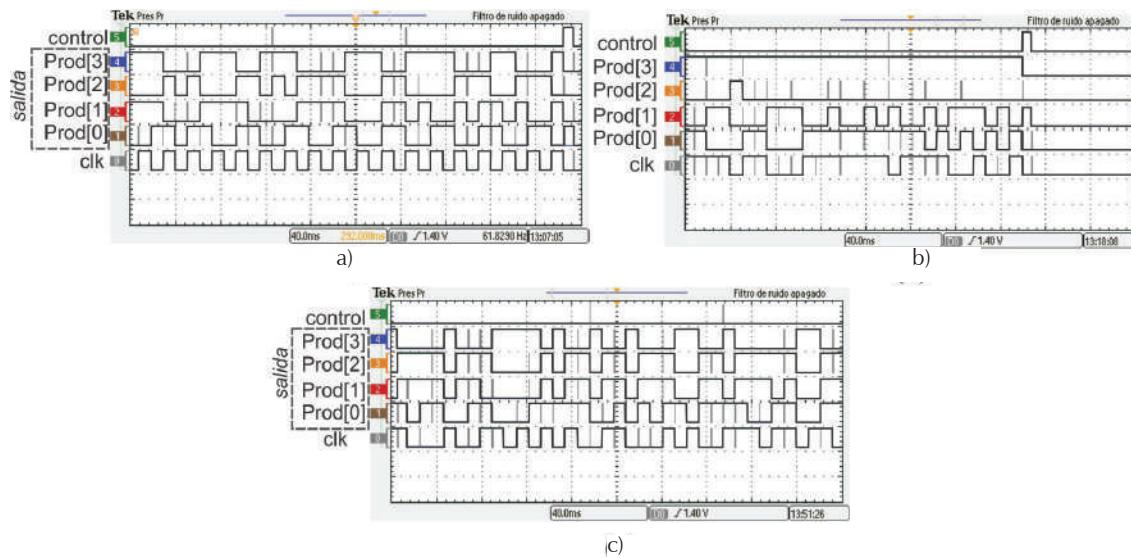

La Figura 10 muestra los resultados experimentales obtenidos en el laboratorio para diferentes secuencias, esto para validar la correcta operación del circuito de salida digital.

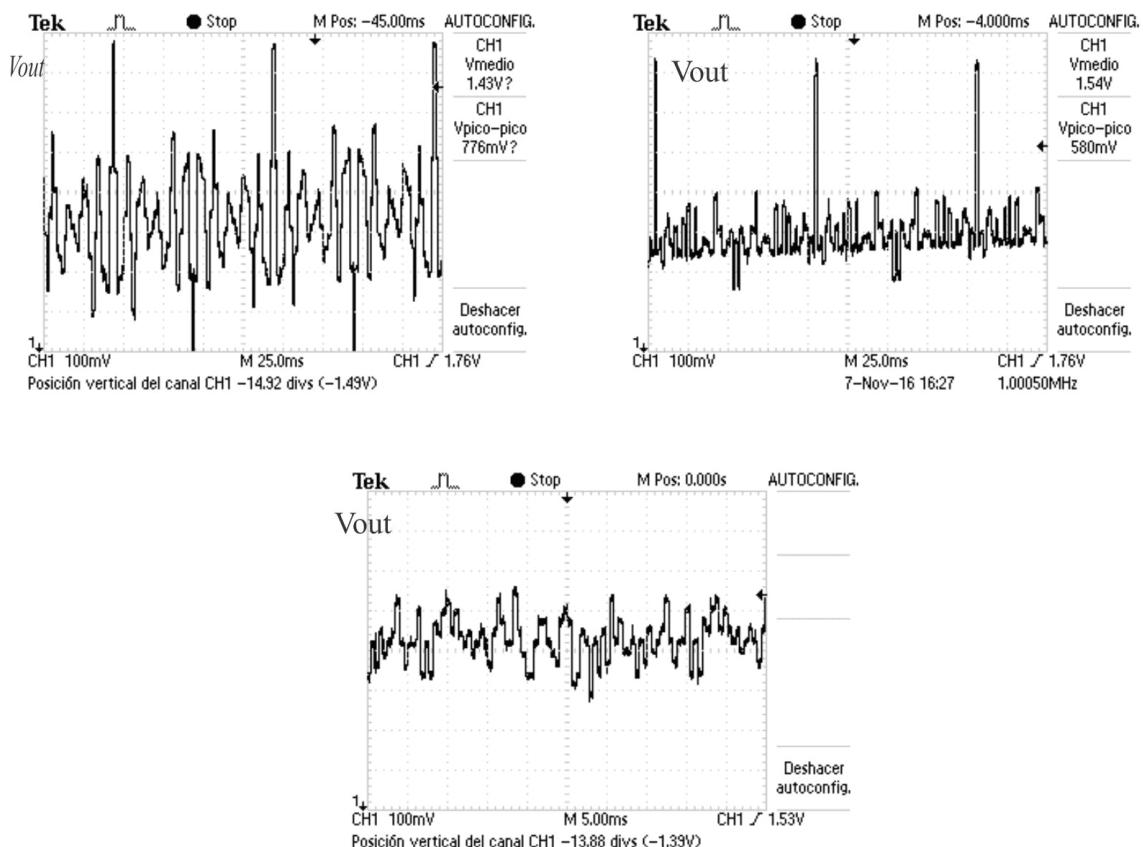

La Figura 11 muestra los resultados obtenidos para diferentes secuencias de entrada y con etapa de salida en formato analógico. La frecuencia de las señales de entrada es de 1 MHz. Verticalmente, el osciloscopio se configura para mostrar 100 mV/div y horizontalmente a 25 ms/div.

Con los resultados obtenidos es posible determinar que el circuito opera correctamente, ya que se sabe que la autocorrelación de dos señales es máxima cuando las señales tienen la misma fase. Esto se ve en los casos a) y b) de las Figuras 10 y 11, respectivamente. Además, cuando las señales son completamente diferentes y no son ortogonales, se detecta un grado de correlación muy bajo, como se indica en la parte c) de las figuras antes mencionadas.

Figura 9. Microfotografía del circuito integrado implementando el correlador de secuencias binarias

Figura 10. Resultados experimentales para la etapa de salida digital para a) dos secuencias de entrada ortogonales, b) entradas aleatorias iguales y c) entradas aleatorias y diferentes

Figura 11. Resultados experimentales para la etapa de salida analógica para la correlación de: a) dos secuencias de entrada mutuamente ortogonales, b) dos secuencias de datos aleatorios pero iguales y c) dos secuencias de datos aleatorios y diferentes (sin correlación)

## CONCLUSIONES

En este documento, se ha discutido una metodología para implementar circuitos integrados con software de muy bajo costo siguiendo un modelo "fabless". Debido a que se siguió este modelo, en ningún momento existió la preocupación por los cuantiosos gastos que implica tener y mantener una fundidora. De esta manera, el trabajo se centró en el diseño del circuito, dejando a The MOSIS Service la construcción del sistema en silicio. Además, debido a que utilizamos herramientas libres, el costo de prototipo se redujo considerablemente. Cabe mencionar que una licencia de software profesional, como CADENCE EDA Tools (<https://www.cadence.com/>), puede alcanzar precios superiores a los 4,000 dólares americanos por año, pero este costo depende de las herramientas que se quieran contratar.

Para validar la metodología discutida, se realizó el diseño de un circuito de procesamiento de señales, el cual fue concebido desde el planteamiento del problema hasta la obtención de resultados experimentales, pasando por los procesos de simulación y validación. Se presentaron las herramientas utilizadas, las cuales son de licencia libre o de muy bajo costo.

Se pretende con esta metodología motivar a los empresarios, ingenieros, investigadores y académicos a desarrollar sus propios productos y entrar al importante sector de la industria electrónica. Sabemos que el posicionamiento de un producto tecnológico es una labor multidisciplinaria, pero nosotros aportamos desde el punto de vista del desarrollo ingenieril, reduciendo algunos de los costos que el prototipado conlleva. La Universidad de Guadalajara, México, ha estado siguiendo esta metodología desde el año 2010 y ha logrado casos de éxito.

## REFERENCIAS

- Alejandro, M.M., Martínez, F.M., Favila, F., García, A. (2016). Historia y evolución de la industria de semiconductores y la integración de México en el sector. *European Scientific Journal*, 12(18), 65-78.

- Baker, R.J. (2010). *CMOS Circuit Design, Layout, and Simulation*. Third Edition. Estados Unidos: Wiley-IEEE Press.

- Brocard, G. (2013). *The LTSpice IV Simulator: Manual, Methods and Applications*. Alemania: Würth Elektronik.

- Chávez, R., García, R., Gurrola, M., Bandala, M. (2015). VLSI Design with Alliance Free CAD Tools: an Implementation example. *Ingeniería Investigación y Tecnología*, 16(3), 441-452. <https://doi.org/10.1016/j.riit.2015.05.007>

- Flores, P. (2013). *Módulo VLSI escalable para la convolución de tramas de bits*. Universidad de Guadalajara, Centro Universitario de Ciencias Exactas e Ingenierías. Guadalajara: Universidad de Guadalajara.

- Hoeren, T. (2016). The Semiconductor Chip Industry-The History, Present and Future of Its IP Law Framework, IIC. *International Review of Intellectual Property and Competition Law*, 47(7), 763-796.

- Liu, W. & Hu, C. (2011). *BSIM4 and MOSFET modeling for IC simulation*. Berkeley. Estados Unidos: World Scientific Publishing Co. Pte. Ltd.

- Maxinez, D. (2013). *Programación de sistemas digitales con VHDL*. México: Editorial Patria.

- PROMEXICO. (2015). Unidad de Inteligencia de Negocios, Diagnóstico Sectorial-Industria Electrónica. Recuperado de <http://www.promexico.gob.mx/documentos/diagnosticos-sectoriales/electronico.pdf>

- Sarma, S. & Li-Sun, S. (2016). The genesis of fabless bussines model: Institutional entrepreneurs in an adaptative ecosystem. *Asia Pacific Journal of Management*, 1-31. <https://doi.org/10.1007/s10490-016-9488-6>

- Sedra, A. & Smith, K. (2014). *Microelectronic circuits*. Oxford, Estados Unidos: O.U. Press, Ed.

- Silva-Cardenas, C., Takeo, Y., Palacios-Pawlovsky, A. (2006). Introduction to VLSI CMOS circuits design. Recuperado el 3 de diciembre de 2019 de Introduction to VLSI CMOS Circuits Design de <http://www.cc.toin.ac.jp/sc/palacios/openbook/vlsie.pdf>