Revista UIS Ingenierías

ISSN: 1657-4583 ISSN: 2145-8456

revistaingenierias@uis.edu.co

Universidad Industrial de Santander

Colombia

Bolívar-Guerrero, Fredy Antonio; L. Díaz, Nelson; Bayona Navarro, Jhon Fredy

Diseño e implementación de un controlador digital tipo PID

con pre-compensación para un Boost PFC de medio puente

Revista UIS Ingenierías, vol. 19, núm. 1, 2020, -Marzo, pp. 179-192

Universidad Industrial de Santander

Bucaramanga, Colombia

DOI: https://doi.org/10.18273/revuin.v19n1-2020017

Disponible en: https://www.redalyc.org/articulo.oa?id=553768131018

Número completo

Más información del artículo

Página de la revista en redalyc.org

Sistema de Información Científica Redalyc

Red de Revistas Científicas de América Latina y el Caribe, España y Portugal Proyecto académico sin fines de lucro, desarrollado bajo la iniciativa de acceso

## Vol. 19, n.° 1, pp. 179-192, 2020

# Revista UIS Ingenierías

# Diseño e implementación de un controlador digital tipo PID con pre-compensación para un Boost PFC de medio puente Design and implementation of a digital PID controller with pre-compensation loop for a half-bridge PFC Boost converter

Fredy Antonio Bolívar-Guerrero<sup>1a</sup>, Nelson L. Díaz<sup>1b</sup>, Jhon Fredy Bayona Navarro<sup>2</sup>

<sup>1</sup>Universidad Distrital Francisco José de Caldas, Bogotá, Colombia. Correos electrónicos: <sup>a</sup> frabolivarg@correo.udistrital.edu.co, <sup>b</sup> nldiaza@udistrital.edu.co <sup>2</sup> Universidad ECCI, Bogotá, Colombia. Correo electrónico: jbayonan@ecci.edu.co

Recibido: 24 octubre, 2019. Aceptado: 9 diciembre, 2019. Versión final: 31 diciembre, 2019.

### Resumen

Este artículo presenta un nuevo método de control para un convertidor Boost con corrección del factor de potencia en configuración de medio puente (CCFP-MPE). En el control propuesto, se adiciona un lazo de pre-compensación que elimina el error en estado estacionario de fase en el control de corriente. Por lo tanto, se logra una mejora en el factor de potencia incluso en condiciones de baja carga y variaciones en el voltaje de la fuente. En el documento se detalla la metodología de diseño del circuito, que incluye, la obtención de la función de transferencia a través del modelo de circuito promedio, el diseño de los controladores que conforman el circuito, el método de eliminación del desbalance de voltaje y el diseño del pre-compensador junto con su análisis, evaluando el efecto en la estabilidad del sistema. Finalmente, se realiza un montaje experimental en el que se definen dos casos de estudio y se presentan los resultados correspondientes, con el fin de validar el controlador propuesto.

Palabras clave: boost de medio puente; corrección de factor de potencia; control PID; pre-compensador.

### **Abstract**

This paper presents a new control method for a Half-Bridge ac-dc Boost converter with power factor correction. The proposed controller includes a pre-compensation loop in order to remove the steady-state phase error in the current control loop. As a consequence, a better power factor is achieved even under soft load conditions or voltage variations in the power source. The paper explores all the stages in the design of the controller, from the derivation of the transfer function, based on an average model, the design of the controllers, a method for eliminating the voltage unbalance in the DC side, the conception and design of the pre-compensation loop, and evaluation of the effect of the precompensation loop in the stability of the system. Finally, the proposed controller is verified experimentally in a real Half-Bridge ac-dc Boost converter which is tested under different operational conditions.

**Keywords:** half-bridge boost converter; power factor correction; PID controller; pre-compensation.

#### 1. Introducción

La electrónica de potencia se ha vuelto parte fundamental de la infraestructura eléctrica actual, debido a que, siendo

una rama de la ingeniería eléctrica, permite suministrar energía a la gran variedad de dispositivos conectados a la red con características particulares de funcionamiento. Esto se logra mediante la conversión de la energía

disponible en los alimentadores a la forma de energía requerida por la carga [1], que pueden ser desde lámparas LED de uso doméstico a tecnologías más complejas como cargadores de baterías para sistemas fotovoltaicos [2], y micro redes eléctricas aplicadas a sistemas eléctricos inteligentes [3].

Actualmente, la gran mayoría de sistemas de distribución funcionan con voltaje AC, por lo que es necesario el uso de convertidores de potencia que sirvan de interfaz para suministrar la energía DC a las cargas electrónicas. Esto se logra a través de convertidores electrónicos y dispositivos como diodos, MOSFETs e IGBTs en conjunto con filtros capacitivos [4]. Estos convertidores presentan un gran problema para las redes de distribución, que consiste en la adición de corrientes armónicas, la inyección de reactivos al sistema y el aumento de la distorsión armónica total THD (por sus siglas en inglés). Adicionalmente, en los casos en que son usados los diodos como rectificadores no es posible regular el voltaje de salida ya que su conmutación no es autónoma [5].

Los circuitos con corrección de factor de potencia (CFP), son la solución propuesta desde la electrónica de potencia para reducir los inconvenientes generados por este tipo de convertidores en el sistema. Los circuitos con CFP permiten limitar las corrientes armónicas al tiempo que disminuyen el valor del THD visto desde la red, mejorando la eficiencia del circuito de conversión [6]. Al final, se logra que la forma de onda de la corriente suministrada por la red presente un comportamiento sinusoidal con un pequeño ángulo de fase entre la forma de onda de la corriente y la forma de onda del voltaje, de modo, que desde el punto de vista de la red la carga se comporta de forma casi resistiva [7].

Se han implementado distintas configuraciones de CFP en los que se ha evaluado su eficiencia bajo condiciones de carga, como el buck-boost en cascada [8], convertidor Cuk [9], circuito Flyback [10] y el convertidor Boost [11] [12], siendo este último el que presenta mayor eficiencia, al tener la capacidad de operar en un amplio rango de cargas tanto en modo continuo como en modo discontinuo [13]. Adicionalmente, existen diversos tipos de circuitos Boost CFP que varían en la cantidad de elementos usados y la disposición de estos, pero principalmente se diferencian por los métodos de control, los modelos de pequeña señal y la cantidad de semiconductores que influyen directamente en otros aspectos del diseño [14]. Dos de las variaciones más usadas son la topología de medio puente (Half-Bridge) y la topología de puente completo (Full-Bridge), las cuales al ser comparadas se observa que la de medio puente brinda un circuito más simple de conversión al usar

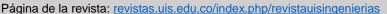

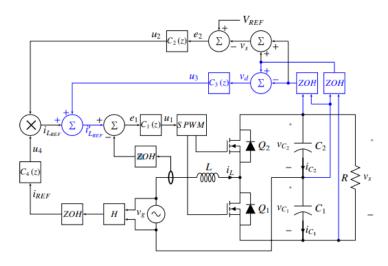

menos dispositivos de conmutación, sin embargo, requiere el uso de un condensador adicional y con mayor capacitancia para obtener valores de rizado similares en el bus DC. De esta manera, la topología de medio puente, como la que se muestra en la Figura 1, logra una mejor eficiencia debido a que un solo dispositivo estaría encendido en un instante de tiempo lo que disminuye las pérdidas [15].

Figura 1. Circuito convertidor AC-DC con corrección de factor de potencia

Para los convertidores Boost CFP con topología de medio puente (Figura 1) el control debe considerar tres aspectos importantes, los cuales son: primero, que la corriente en la fuente AC pueda seguir la forma de onda del voltaje, reduciendo el ángulo de fase entre ellas y acercando el factor de potencia a la unidad; segundo, asegurar una correcta conversión de AC/DC manteniendo la salida en rangos admisibles sin grandes variaciones que puedan perjudicar la carga [16]; y tercero, disminuir el desbalance de voltaje presente en los en condensadores del lado DC [17].

Sin embargo, es posible analizar los anteriores aspectos de forma separada, debido a que cada uno puede implementar una estrategia de control independiente. En el caso de la corriente en la fuente, es posible controlarla por medio de las variaciones del sensor aplicado, debido a que cada uno va a tener una respuesta específica dependiendo de la frecuencia a la que trabajen los dispositivos de conmutación, siendo así, que la respuesta del aislamiento del sensor también afectará la banda de trabajo del PFC en topología de medio puente [18].

Distintas técnicas de control se han estudiado en la literatura las cuales por su construcción sirven para casos específicos de aplicación, algunos de estos son: control de corriente pico [19], control promedio de corriente [20], control por histéresis [21], control por borderline

[22], controles predictivos [23] y control de corriente discontinua con PWM [24] [25].

En este artículo, se lleva a cabo el diseño y la implementación de un convertidor con corrector de factor de potencia en configuración de medio puente elevador (CCFPMPE), en el que se presenta un nuevo método de control mediante la implementación de un controlador digital tipo PID con pre-compensación. De esta forma se elimina el error en estado estacionario y aumenta la estabilidad del sistema. La validación de resultados se realiza por medio de un montaje experimental.

La sección 2 de este artículo presenta el modelo usado para definir el estado estacionario del circuito del CCFP-MPE así como su función de transferencia y parámetros. En la sección 3, se describen los controladores del CCFPMPE junto con la metodología seguida para su sintonización e implementación digital. La sección 4, muestra los resultados experimentales sobre las variables de interés y la sección 5 las conclusiones

## 2. Modelo y función de transferencia del CCFP-MPE

El CCFP-MPE es un convertidor AC-DC que está compuesto de dos interruptores tipo MOSFET (Q1 y Q2), cada uno de ellos con sus diodos intrínsecos, dos condensadores ( $C_1$  y  $C_2$ ), una inductancia (L) y una carga resistiva (R), como se muestra en la Figura 1.

Es posible definir las ecuaciones de estado del circuito que relacionan el ciclo útil d del período de conmutación de los MOSFET, considerando las pérdidas a través del modelo de circuito promedio, y teniendo en cuenta la diferencia de voltaje entre los dos condensadores  $(v_d)$ , de acuerdo a como se presenta en [26]. Dichas ecuaciones se expresan como:

$$\frac{di_L}{dt} = \left(\frac{r_L + r_{DS}}{L}\right) i_L + \frac{1}{2L} v_d + \left(\frac{2d-1}{2L}\right) v_S + \frac{1}{L} v_g$$

(1)

$$\frac{dv_s}{dt} = -\left(\frac{2d-1}{C}\right)i_L - \frac{2}{RC}v_s \tag{2}$$

$$\frac{dv_d}{dt} = -\frac{1}{c} i_L \tag{3}$$

Dónde, los parámetros de las ecuaciones y sus respectivos valores de operación en estado estacionario se relacionan en la tabla 1.

El tiempo de muestreo se seleccionó de acuerdo a las recomendaciones prácticas típicamente utilizadas para este tipo de convertidores, en las cuales, se espera realizar la acción de control dentro del tiempo para la actualización de la señal del PWM en el procesador [27].

Por otro lado, el proceso de selección de los demás parámetros es detallado en [26].

Tabla 1. Parámetros de circuito del CCFP-MPE

| Símbolo     | Parámetro                              | Valor                |

|-------------|----------------------------------------|----------------------|

| $C=C_1=C_2$ | Condensadores de la salida DC          | 100μ <i>F</i>        |

| L           | Inductor                               | 5mH                  |

| $r_L$       | Perdidas en el cobre de la inductancia | 0,2Ω                 |

| $r_{DS}$    | Resistencia de los<br>MOSFETs          | 0,85Ω                |

| R           | Carga resistiva                        | 2kΩ                  |

| $v_{gRMS}$  | Voltaje de línea                       | 120 V                |

| $i_{LRMS}$  | Corriente en el inductor               | 0,84 A               |

| ω           | Frecuencia angular                     | 376,9 <sup>rad</sup> |

| f           | Frecuencia de la línea                 | 60 Hz                |

| $T_s$       | Periodo de conmutación                 | $20\mu s$            |

| $T_m$       | Tiempo de muestreo                     | $20\mu s$            |

| $v_p$       | Voltaje pico de la línea               | $120 \sqrt{2} V$     |

| $I_p$       | Corriente pico del inductor            | 1,2 A                |

| $v_d$       | Diferencia de voltaje a la salida      | 0 V                  |

| $v_s$       | Suma de voltaje a la<br>salida         | 460 V                |

Posteriormente, se linealizan las ecuaciones (1), (2) y (3), obteniendo como resultado la función de transferencia del CCFP-MPE:

$$G_S = \frac{i_{L(S)}}{d_{(S)}} = \frac{\frac{v_S}{L}S^2 + \frac{2v_S}{RLC}S}{S^3 + K_2S^2 + K_1S + \frac{1}{PLC^2}},$$

(4)

donde, las constantes  $K_1$ , y  $K_2$ , son definidas así:

$$K_1 = \frac{2I^2 p \omega^2 L}{v_s^2 C} + \frac{1}{2LC} + \frac{2(r_L + r_{DS})}{RLC}$$

(5)

$$K_2 = \frac{r_L + r_{DS}}{L} + \frac{2}{RC} \tag{6}$$

Al reemplazar las variables de la Tabla 1, G(s) se reescribe como:

$$G_{s} = \frac{90000s^{2} + 90000s}{s^{3} + 220s^{2} + 1,002 \times 10^{6}s + 1 \times 10^{7}}$$

(7)

Mediante el método de retención de orden cero (ZOH), se discretiza G(s):

$$G_{(Z)} = \frac{1,796Z^{2} - 3,592Z + 1,796}{Z^{3} - 2,995Z^{2} + 2,991Z - 0,9956}$$

(8)

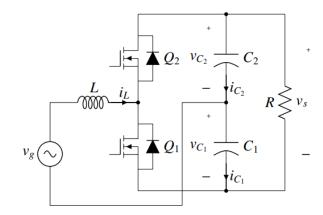

Debido a que el ciclo útil se carga en el siguiente periodo de conmutación, como se muestra en la Figura 2, se debe considerar el retardo ( $z^{-1}$ ). Por esta razón, la función de

transferencia definida por la ecuación (8), se convierte en:

$$T_{(Z)} = \frac{1,796z^2 - 3,592z + 1,796}{z^4 - 2,995z^3 + 2,991z^2 - 0,9956z} \tag{9}$$

Es decir que (9) corresponde a la ganancia de lazo de corriente en el CCFP-MPE con el retardo incluido.

Figura 2. Tiempo de retardo entre el cálculo y la carga del ciclo útil

### 3. Lazos de control del CCFP-MPE

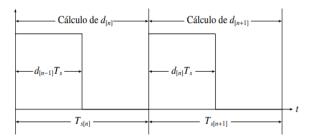

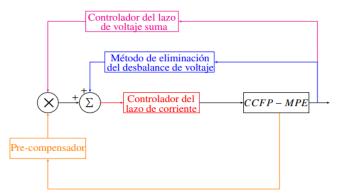

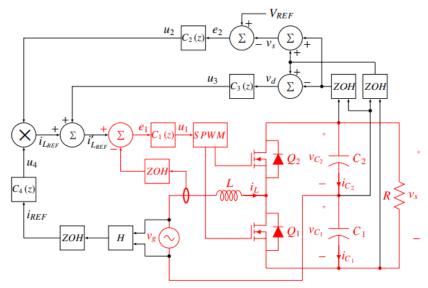

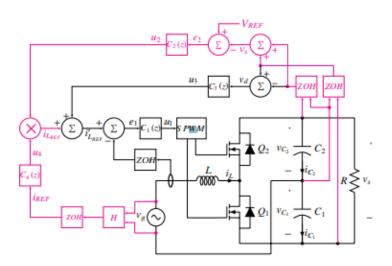

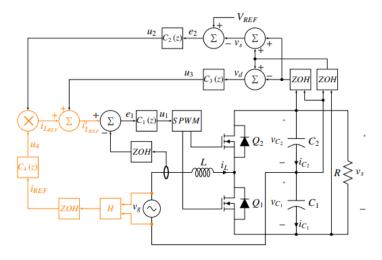

En la Figura 3, se muestra el esquema de control del CCFP-MPE, el cual es representado como un diagrama de bloques en la Figura 4. La arquitectura de control consta de dos lazos. El primero, es el controlador de corriente que obliga a  $i_L$  a seguir la forma de onda de  $v_g$ , para aumentar el FP. El segundo, es el controlador de voltaje suma que regula vs a un valor constante predefinido. Además, cuenta con un método de eliminación del desbalance de voltaje en  $C_1$  y  $C_2$  que mantiene  $v_d$  cercano a cero y un pre-compensdor que reduce el error en estado estacionario y aumenta la estabilidad del sistema.

## 3.1. Controlador del lazo de corriente

El lazo del controlador de corriente que se muestra en la Figura 5 resaltado, está compuesto por el CCFP-MPE y

Figura 3. Diagrama de control del CCFP-MPE

Figura 4. Diagrama de control del CCFP-MPE

Figura 5. Diagrama de control del CCFP-MPE, lazo de corriente

Figura 6. Diagrama de control PIDF del lazo de corriente del CCFP-MPE

el controlador de corriente  $(C_I(z))$ , este lazo de control tiene como propósito que  $i_L$  siga la forma de onda de  $i^0_{LREF}$  definida por el lazo de voltaje suma, para obtener un factor de potencia cercano a la unidad.

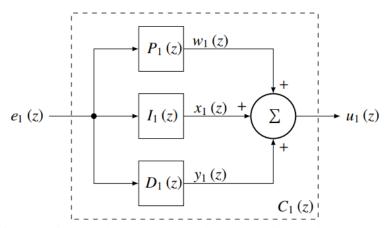

$C_I(\mathcal{Z})$  es un controlador tipo PIDF en paralelo el cual se muestra en la Figura 6 y está definido por:

$$C_{1(Z)} = \frac{u_1(Z)}{e_1(Z)} = P_1(Z) + I_1(Z) + D_1(Z), \quad (10)$$

donde,  $P_1$  (Z),  $I_1$  (Z) y  $D_1$  (Z) son las ganancias proporcional, integral y derivativa respectivamente. En el caso de  $I_1$  (Z) se usa el método de discretización trapezoidal mientras que en  $D_1$  (Z) se usa el método backward, debido a que el uso del mismo método en

ambos, hace que el derivador se vuelva inestable [28], por ende, las ganancias están dadas por:

$$P_1(Z) = \frac{w_1(Z)}{e_1(Z)} = K_{P_1} \tag{11}$$

$$I_1(Z) = \frac{x_1(Z)}{e_1(Z)} = K_{I_1} \left(\frac{T_s}{2}\right) \left(\frac{Z+1}{Z-1}\right)$$

(12)

$$D_1(\mathcal{Z}) = \frac{y_1(\mathcal{Z})}{e_1(\mathcal{Z})} = K_{D_1}\left(\frac{1}{T_f + T_S\left(\frac{\mathcal{Z}}{\mathcal{Z} - 1}\right)}\right) \tag{13}$$

Se divide el denominador y numerador de (12) y (13) por z; luego, se resuelve  $W_1(Z)$ ,  $X_1(Z)$  y  $y_1(Z)$ ; finalmente, se aplica la transformada z inversa, para obtener las ecuaciones en diferencia que se muestran a continuación:

$$W_1[n] = K_{P_1} e_1[n] \tag{14}$$

$$\mathcal{X}_{1}[n] = \mathcal{X}_{1}[n-1] + K_{I_{1}}\left(\frac{T_{5}}{2}\right)(e_{1}[n] + e_{1}[n-1])$$

(15)

$$y_{1}[n] = \left(\frac{T_{f}}{T_{f} + T_{S}}\right) y_{1}[n-1] + \left(\frac{K_{D_{1}}}{T_{f} + T_{S}}\right) (e_{1}[n] - e_{1}[n-1])$$

(16)

La constante proporcional  $(K_{p_1})$  entrega la ganancia del controlador que, dependiendo de su valor estabiliza o no el sistema; la constante integral  $(K_{I_1})$  disminuye el error en estado estacionario y mejora la estabilidad relativa; la constante derivativa  $(K_{D_1})$  aumenta la estabilidad de la planta y reduce el sobre impulso, así mismo, el tiempo de filtro  $(T_f)$  evita que la acción derivativa amplifique el ruido [28], [29], [30]. Para definir el valor de las constantes del controlador  $C_I$  (z) se sintoniza con la aplicación PID Tuner de MATLAB®, seleccionando el modelo PIDF (acción de control proporcional integral derivativo con filtro), con los parámetros  $Response\ Time\ y\ Transient\ Behavior\ de\ 131.5\ \mus\ y\ 0.58\ s$  respectivamente, como resultado, las constantes de  $C_I$  (z) son  $(K_{p_1})=0.295, (K_{I_1})=1.28\times103, (K_{D_1})=7.4\times10-6\ y\ T_f=1.67\times10-5$  .

## 3.2. Controlador del lazo de voltaje suma

Se puede observar en la Figura 7, resaltado el lazo del voltaje suma, dentro del cual, se encuentra su controlador  $C_2(z)$ , este lazo de control es el encargado de mantener

$v_S$  en un valor constante que está definido por  $V_{REF}$ . Para lograr que  $v_S$  se mantenga constante, se debe mantener el valor pico de  $i_{L_{REF}}$  constante, dado que,  $v_S$  es directamente proporcional a este valor pico. Por esta razón, se conecta la salida del controlador  $C_2(z)$ , al bloque multiplicador como se ilustra en la Figura 7, como resultado,  $C_2(z)$  gobierna el valor pico de  $i_{L_{REF}}$  y simultáneamente a  $v_S$ .

En [26] se mencionó que la dinámica del lazo de corriente es rápida, causando que la demanda de potencia a  $v_g$  sea prácticamente instantánea en comparación con la potencia entregada a R. Por consiguiente, sólo la dinámica del lazo del voltaje suma necesita ser considerada, para obtener la función de transferencia que describe su comportamiento y así poder diseñar su controlador. También, en [26] se propuso la función de transferencia del lazo del voltaje suma como:

$$G_{vs}(S) = \frac{v_s(S)}{u_2(S)} = K_{D_1} \left( \frac{\frac{V_P - 2(r_L + r_{DS})I_P}{V_S C}}{S + \frac{2}{RC}} \right), \tag{17}$$

siendo  $u_2$  (s) la salida de  $C_2$  (z), como se ilustra en la Figura 7. Sustituyendo en (17) los parámetros de circuito del CCFP-MPE que se encuentran en la Tabla 1, entonces:

$$G_{vs}(S) = \frac{_{3727}}{_{S+10}} \tag{18}$$

Usando el método de discretización *ZOH*, la función de transferencia que define el lazo de voltaje suma es:

$$G_{vs}(z) = \frac{0.07454}{z - 0.9998} \tag{19}$$

Figura 7. Diagrama de control del CCFP-MPE, lazo de voltaje suma

Figura 9. Diagrama de control del CCFP-MPE, lazo del método de eliminación del desbalance de voltaje

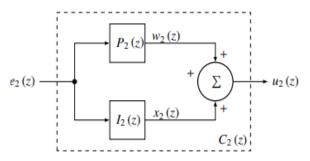

A partir de  $G_{vs}(z)$ , se sintoniza  $C_2(z)$ como un controlador tipo PI en paralelo como se muestra en la Figura 8.

Figura 8. Diagrama de control PIDF del lazo de voltaje suma del CCFP-MPE

El controlador  $C_2(z)$  se expresa como la suma de la acción proporcional  $(P_{2(Z)})$  y la integral  $(I_{2(Z)})$ , entonces:

$$C_2(z) = \frac{u_2(z)}{e_2(z)} = P_2(z) + I_2(z),$$

(20)

donde,  $P_2(Z)$  e  $I_2(Z)$  son las ganancias proporcional e integral respectivamente, para  $I_2(Z)$  se usa el método de discretización trapezoidal.

$$P_{2(Z)} = \frac{w_2(Z)}{e_2(Z)} = K_{P_2}$$

(21)

$$I_2(Z) = \frac{\chi_2(Z)}{e_2(Z)} = K_{I_2} \left(\frac{T_S}{2}\right) \left(\frac{Z+1}{Z-1}\right)$$

(22)

Se pueden escribir (21) y (22) como ecuaciones en diferencia, obteniendo;

$$\mathcal{W}_2[n] = K_{P_2} e_2[n] \tag{23}$$

$$\mathcal{X}_{2}[n] = \mathcal{X}_{2}[n-1] + K_{I_{2}}\left(\frac{T_{s}}{2}\right)(e_{2}[n] + e_{2}[n-1])$$

(24)

Los valores de las constantes del controlador  $C_2(z)$  se encuentran usando PID Tuner de MATLAB®a partir de los parámetros *Response Time y Transient Behavior* ajustando los valores donde la planta en lazo cerrado es estable, logrando esto en 0.11 s y 0.37 s respectivamente. Como resultado, las constantes de  $C_2(\mathcal{Z})$  son  $K_{P_2}$  de 0,00065 y  $K_{I_2}=0,092$ .

# 3.3. Método de eliminación del desbalance de voltaje en $C_1$ y $C_2$

La referencia [14], explicó la causa del desbalance de voltaje en los condensadores y sugirió un método para eliminarlo que consiste en sumar a la corriente de referencia  $i_{L_{REF}}$  la diferencia de voltaje entre los dos condensadores  $(v_d)$  multiplicada por la ganancia del controlador  $C_3(Z)$ . Este método se observa en la Figura 9 resaltado; así mismo, en [14] definen el valor de la ganancia de  $C_3(Z)$ .como:

$$C_3(z) = \frac{u_3(z)}{e_3(z)} = 0.1\omega C$$

(25)

Se resuelve  $u_3(Z)$  y se aplica la transformada z inversa, por consiguiente, la ecuación en diferencia resultante es:

Figura 10. Diagrama de control del CCFP-MPE, precompensador

$$u_3[n] = 0.1\omega C v_d[n] \tag{26}$$

De ahí que, la nueva corriente de referencia está dada por:

$$i'_{L_{RFF}}[n] = i_{L_{RFF}}[n] + 0.1\omega C v_d[n]$$

(27)

## 3.4. Pre-compensador

En (7) se observa que existe un cero en el origen que elimina el efecto del integrador de  $C_1(Z)$ . Por esta razón, no se puede reducir el error en estado estacionario, además, la corriente  $i_L$  no puede seguir exactamente a  $i'_{LREF}$ , de ahí que,  $i_L$  está dada por:

$$i'_{L_{RFF}} = I_P \sin(\omega t + \emptyset), \tag{29}$$

donde  $\emptyset$  es el desplazamiento producido por la existencia del error en estado estacionario y su valor es mayor a cero. En consecuencia, se debe desplazar  $i'_{L_{REF}}$  a un valor de  $-\emptyset$ , para anular el desplazamiento en  $i_L$ , entonces:

$$i'_{L_{RFF}} = u_2 u_4 + u_3, (30)$$

donde  $u_2$ ,  $u_3$  y  $u_4$  son las salidas de  $C_2(\mathcal{Z})$ ,  $C_3(\mathcal{Z})$ , y del pre-compensador  $C_4(\mathcal{Z})$  respectivamente. Sin embargo, para el diseño de  $C_4(\mathcal{Z})$ , se considera unicamente la dinámica del lazo de corriente asumiendo que  $u_2$ es igual a uno y  $u_3$  es nulo, por tanto, (30) se convierte en:

$$u_4 = i'_{L_{REF}} = I_P \sin(\omega t + \emptyset) \tag{31}$$

También, se puede ver en la Figura 10 que  $i_{L_{REF}}$  es proporcional a  $v_g$  y es igual a:

$$i_{L_{REF}} = H \nu_g \tag{32}$$

El diseño de  $C_4(Z)$  se realiza en tiempo continuo y posteriormente se transforma a tiempo discreto. Es por esto que  $C_4(s)$  debe ser una red de atraso, puesto que,  $i'_{LREF}$  está en atraso  $\emptyset$  radianes con respecto a  $i_{LREF}$ , por lo cual,  $C_4(s)$  está dado por:

$$C_4(s) = \frac{\kappa}{s + \alpha},\tag{33}$$

sustituyendo s por  $j\omega$  en (33) y expresándola en forma polar, se obtiene:

$$C_4(j\omega) = \frac{\kappa}{\sqrt{\omega^2 + \alpha^2}} / \underline{-\beta}, \qquad (34)$$

donde

$$\beta = \tan^{-1}\left(\frac{\omega}{\sigma}\right) \tag{35}$$

Resolviendo  $\alpha$  de (35) y reemplazando en (34), entonces:

$$C_4(j\omega) = \frac{K \sin(\emptyset)}{\omega} / \underline{\beta}, \qquad (36)$$

Convirtiendo al dominio de la frecuencia a (31) y (32), se obtiene:

$$\mathbf{U}_{4} = I_{P} / - \emptyset \tag{37}$$

$$I_{REF} = HV_P \tag{38}$$

Al observar la Figura 10, se deduce que:

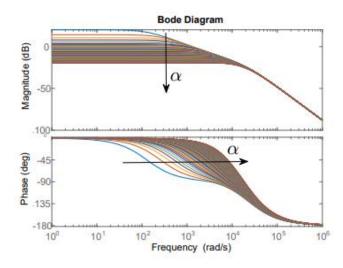

Figura 11. Diagrama de bode para distintos valores de α

Figura 12. Diagrama de bode para distintos valores de  $\kappa$

$$\mathbf{U}_{4} = C_{4} \ (j\omega) \ \mathbf{I}_{REF} = \frac{kHV_{P} \sin(\emptyset)}{\omega} / \underline{\beta}$$

(39)

De 37 y 39 se iguala magnitud con magnitud, así como fase con fase, lo que produce como resultado:

$$\beta = \emptyset \tag{40}$$

$$I_p = \frac{kHV_P \sin(\emptyset)}{\omega} \tag{41}$$

Resolviendo (35) y (41), se encuentran los valores de  $\alpha$  y k que son respectivamente 1285 y 1332.5, por otro lado, al transformar de tiempo continuo a discreto, (33) se convierte en:

$$C_4(Z) = \frac{u_4(Z)}{i_{REF}(Z)} = \frac{kT_S}{Z + \alpha T_S - 1}$$

(42)

Aplicando la transformada  $\mathcal{Z}$  inversa a (42), se obtiene la siguiente ecuación en diferencia:

$$u_4[n]=kT_si_{REF}[n-1]-(\propto T_s-1)u_4[n-1]$$

(43)

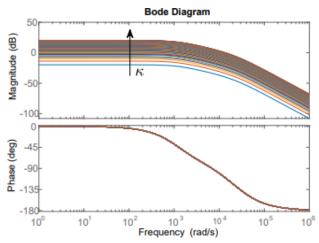

# 3.5. Efecto del pre-compensador en la estabilidad del sistema

Para verificar el efecto del pre-compensador, en la estabilidad del sistema realimentado, se realizaron variaciones de los parámetros  $\alpha$  y  $\kappa$ , en un rango de 0.1 a 10 veces el valor de diseño. La Figura 11 muestra el comportamiento del sistema con la variación de  $\alpha$ , y la Figura 12 muestra el comportamiento del sistema

realimentado con pre-compensador para la variación de  $\kappa$ . De las figuras se puede deducir que no se ve comprometida la estabilidad del sistema. Sin embargo, la elección de estos parámetros resulta crítica en el error de estado estacionario del sistema con pre-compensador tanto en magnitud como en fase.

### 4. Resultados

En la Figura 13 se muestra el montaje experimental del CCFP-MPE que está constituido por una variación, una carga variable con resistencias en paralelo y dos osciloscopios de Agilent Technologies U1620A para la visualización y registro de datos. Como dispositivo de control se implementó un controlador digital con el DSP de Texas Instruments TMDX28069USB, tarjeta también conocida como Piccolo F28069.

El circuito impreso está compuesto por una inductancia de núcleo de ferrita con formaleta de referencia EA77-625, transistores STP13NK60ZFP de ST Microelectronics, condensadores electroliticos de 250V y el integrado HCPL-3120 como driver de disparo para los semiconductores. La medición de la forma de onda de la corriente de la inductancia se realiza con el sensor LEM HAS50-S mediante efecto Hall, mientras, que la medición de voltajes se realiza por medio de amplificadores operacionales en modo diferencial.

Figura 13. Montaje experimental

En la Figura 14 se puede observar la forma de onda de  $v_{C_1}$  y  $v_{C_2}$  del CCFP-MPE en condiciones normales de operación. Se puede determinar que el desbalance de voltaje es mínimo con un valor de 208mV.

Con el propósito de comprobar el comportamiento del CCFP-MPE bajo distintas condiciones de operación se definieron dos casos de estudio: respuesta en estado transitorio y respuesta en estado estacionario.

Figura 14. Forma de onda en los condensadores de salida a plena carga

# 4.1. Resultado de las pruebas en estado transitorio

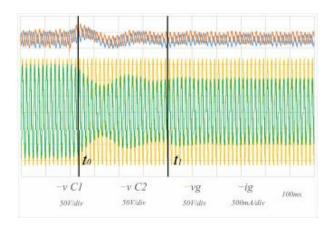

La respuesta del CCFP-MPE en estado transitorio cuando hay un aumento en escalón de 120V a 140V es mostrado en la Figura 15, la duración del transitorio es de 180ms entre  $t_0$  y  $t_1$ , y el sobre pico de  $v_{C_1}$  y  $v_{C_2}$  es de 18V. Similarmente, la reducción en escalón de 140V a 120V se observa en la Figura 16, el período del transitorio entre  $t_0$  y  $t_1$  es de 75ms, y la caída de  $v_{C_1}$  y  $v_{C_2}$  es de 10V. De igual forma, la respuesta transitoria cuando se disminuye la carga de 100 % a 70 % de su valor nominal es mostrada en la Figura 17, en la que se observa la duración del periodo transitorio alrededor de 370ms entre  $t_0$  y  $t_1$ , y la caída de  $v_{C_1}$  y  $v_{C_2}$  de 13V. Igualmente, el aumento de carga de 70 % a 100 % es mostrado en la Figura 18, con la duración del transitorio entre  $t_0$  y  $t_1$  de 90ms y un sobre pico alrededor de 11V en  $v_{C_1}$  y  $v_{C_2}$ .

Figura 15. Señal de  $v_{\mathcal{C}_1}$ ,  $v_{\mathcal{C}_2}$ , vg e ig durante el cambio de 120Vrms a 140Vrms

Figura 16. Señal de  $v_{C_1}$ ,  $v_{C_2}$ , vg e ig durante el cambio de 140Vrms a 120Vrms

Figura 17. Señal de  $v_{\mathcal{C}_1},\ v_{\mathcal{C}_2}$  , vg e ig durante la transición de 100 % a 70 % de carga

Figura 18. Señal de *vg* e *ig* durante la transición de 70 % a 100 % de carga

En las Figuras 15-18 se puede apreciar la forma de onda sinusoidal de la corriente *ig*, durante y después de los transitorios, por el efecto del pre-compensador al poder

seguir exactamente la forma de onda de vg. Adicionalmente, se observa que el método de eliminación del desbalance de voltaje en  $C_1$  y  $C_2$  mantiene una diferencia mínima entre  $v_{C_1}$  y  $v_{C_2}$  y el controlador de voltaje suma retorna  $v_s$  a un valor cercano a  $V_{REF}$ .

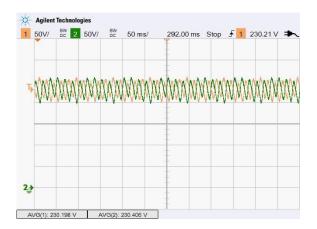

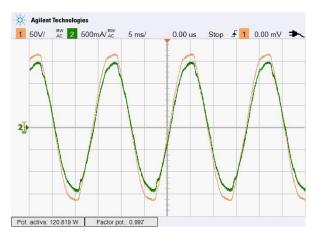

# 4.2. Resultado de las pruebas en estado estacionario

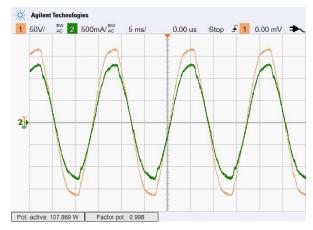

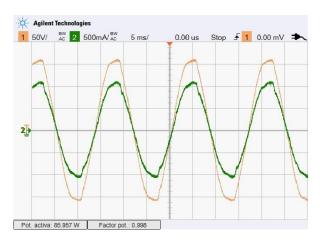

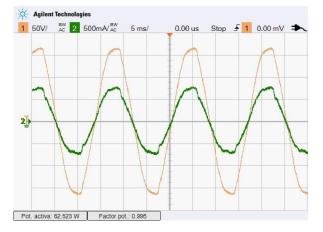

Las formas de onda de vg e ig en estado estacionario con máxima carga de 100 % son mostradas en la Figura 19, la potencia activa es de 120.819W y el FP es 0.997. Las formas de onda de vg e ig para la condición de carga del 90 % son mostradas en la Figura 20, la potencia activa es de 107.869W y el FP es de 0.998. Las formas de onda de vg e ig para el 70 % de la carga son mostradas en la Figura 21, la potencia activa con esta condición de carga es de 85.957W y el FP es de 0.998. Las formas de onda de vg e ig para el 50 % de la carga son mostradas en la Figura 22, para esta condición de carga la potencia activa es de 62.523W y el FP es de 0.995.

Figura 19. Forma de onda de vg e ig al 100 % de carga

Figura 20. Forma de onda de vg e ig al 90 % de carga

El FP alto visto en las Figuras 19-22 para los diferentes porcentajes de carga muestra el correcto funcionamiento del lazo del pre-compensador en estado estacionario, además, la disminución del porcentaje de carga no afecta el FP en gran medida, debido a que el pre-compensador mantiene el FP cercano a la unidad hasta en un caso crítico como tener el 50 % del valor nominal de carga en la Figura 22. Por otro lado, la forma de onda observada de *ig* es sinusoidal en cada una de las pruebas.

En la tabla 2 se realiza la comparación de resultados entre el método de control propuesto para el CCFP-MPE con pre-compensación y otro trabajo reportado anteriormente en [15], en el que se implementó el método de control de portadora no lineal. Al observar la tabla 2 se puede aseverar lo siguiente: Primero, el FP del CCFP-MPE con el método propuesto es mayor que el obtenido en [15]. Segundo, la respuesta trsnsitoria con el método de control propuesto para el CCFP-MPE es más rápida que la presentada en [15]. Por último, la caída de voltaje en los condensadores es igual en ambos métodos.

Figura 21. Forma de onda de vg e ig al 70 % de carga

Figura 22. Forma de onda de vg e ig al 50 % de carga

Tabla 2. Comparación de desempeño entre el método de control propuesto y otro trabajo.

| Parámetro                                 | [15]   | CCFP-<br>MPE |

|-------------------------------------------|--------|--------------|

| Frecuencia de conmutación (kHz)           | 10     | 50           |

| Voltaje de entrada ( $V_{AC}$ )           | 106    | 120          |

| Potencia (W)                              | 800    | 120          |

| Factor de potencia                        | 0.98   | 0.998        |

| Tiempo de transitorio (ms)                | 300    | 90           |

| Caída de voltaje en los condensadores (V) | 10     | 10           |

| Cambio de carga ( %)                      | 75-100 | 70-100       |

#### 5. Conclusiones

El esquema de pre-compensación propuesto logra su propósito de reducción de error de estado estacionario, logrando mantener el factor de potencia cercano a la unidad aun cuando la elección de sus parámetros resulte crítica para el error de magnitud y fase. Adicionalmente, posibles variaciones en los parámetros no comprometen la estabilidad del sistema.

Con el resultado de las pruebas, se observó que aumenta la fiabilidad del circuito al poder responder ante eventos como sobretensiones, y disminución o aumento de carga de forma continua, sin perjudicar su funcionamiento. Esto permitirá su aplicación en sistemas que demanden mayor potencia o que impliquen el manejo y control de cargas especiales.

Debido a que durante periodos prolongados de funcionamiento se obtuvieron valores constantes de 460.604*V* sobre la carga, con una potencia de 120*W* y FP de 0.998, es posible realizar su implementación en sistemas más complejos y de trabajo continuo bajo la metodología seguida en el presente artículo, En estos casos, la única diferencia será la selección de dispositivos con la capacidad adecuada para la aplicación requerida.

En las pruebas de estado estacionario se demostró el beneficio del efecto del lazo del pre-compensador en el sistema, al lograr que la forma de onda de corriente de la fuente siguiera la forma de onda del voltaje de la fuente, de modo que, la corriente tiene una forma de onda sinusoidal y así mantiene un FP alto para un amplio rango de porcentajes de carga.

# Agradecimientos

Este trabajo hace parte del proyecto de investigación 2-7-563-17 financiado por el Centro de Investigaciones y Desarrollo Científico de la Universidad Distrital Francisco José de Caldas. A los laboratorios de la

Facultad de Ingeniería de la universidad ECCI (Escuela Colombiana de Carreras industriales), donde fue posible realizar los ensayos de diseño y pruebas finales.

### Referencias

- [1] A. Shukla y M. Kumar Pradhan, "A neural network controller for high power factor in fly back converters," en 2016 International Conference on Research Advances in Integrated Navigation Systems (RAINS), Bangalore, India, 2016.

- [2] F. Jauch y J. Biela, "Combined phase-shift and frequency modulation of a dual-active-bridge ac-dc converter with pfc," *IEEE Transactions on Power Electronics*, vol. 31, pp. 8387 8397, 2016.

- [3] J. Rocabert, A. Luna, F. Blaabjerg, y P. Rodríguez, "Control of power converters in ac microgrids," *IEEE Transactions on Power Electronics*, vol. 27, no. 11, pp. 4734–4749, Nov 2012.

- [4] A. Pereira, J. Vieira, y L. Freitas, "A lossless switching forward converter with unity power factor operation," in Proceedings of IECON '95 21st Annual Conference on IEEE Industrial Electronics IEEE, Orlando, USA, 1995.

- [5] C.-Y. Hung, J.-C. Wu, Y.-L. Chen, y H.-L. Jou, "A gridconnected battery charger with power factor correction," in 2016 IEEE 11th Conference on Industrial Electronics and Applications (ICIEA), Hefei, China, 2016.

- [6] M. Bodetto, A. E. Aroudi, A. Cid-Pastor, J. Calvente, and L. M. Salamero, "Design of ac dc pfc high-order converters with regulated output current for low-power application," *IEEE Transactions on Power Electronics*, vol. 31, pp. 2012 2025, 2016.

- [7] J. P. Noon, "Designing high-power factor off-line power supplies," in *TI Literature* No. SLUP203, 2003.

- [8] B.-G. Kang, C.-E. Kim, J. Black, D.-K. Kim, y G.-W. Moon, "A high power density and power factor cascade buck-boost pfc under expanded high line voltage," in 2016 IEEE Transportation Electrification Conference and Expo, Asia-Pacific (ITEC AsiaPacific), Busan, South Korea, 2016.

- [9] V. Sheela y M. Gopinath, "Effiency analysis of bridgeless cuk converter for pfc applications," in 2013 International Conference on Information Communication and Embedded Systems (ICICES), Chennai, India, 2013.

- [10] X. Xie, J. Li, K. Peng, C. Zhao, y Q. Lu, "Study on the singlestage forward-flyback pfc converter with qr control," IEEE Transactions on Power Electronics, vol. 31, pp. 430 442, 2016.

- [11] D. Sun, S. Xu, W.-f. Sun, y S. Lu, "A new digital predictive control strategy for boost pfc converter," *IEICE Electronics Express*, vol. 12, pp. 1 8, 2015.

- [12] R. Blundell, L. Kupka, y S. Spiteri, "Ac-dc converter with unity power factor and minimum harmonic content of line current: design considerations," *IEE Proceedings Electric Power Applications*, vol. 145, pp. 553 558, 1998

- [13] N. A. Dung, P. P. Hieu, H.-J. Chiu, Y.-C. Hsieh, y J.-Y. Lin, "A new digital control strategy of boost pfc at high-line light-load condition," in 2016 IEEE International Conference on Industrial Technology (ICIT), Taipei, Taiwan, 2016.

- [14] R. Srinivasan y R. Oruganti, "A unity power factor converter using half-bridge boost topology," *IEEE Transactions on Power Electronics*, vol. 3, pp. 487 500, 1998

- [15] R. Ghosh y G. Narayanan, "A simple analog controller for single-phase half-bridge rectifier," *IEEE Transactions on Power Electronics*, vol. 22, no. 1, pp. 186–198, 2007.

- [16] I. Lachkar, F. Giri, A. Abouloifa, y F. Z. Chaoui, "Nonlinear pwm controller for a single-phase half bridge ac-dc converters," in 2014 European Control Conference (ECC), 2014, pp. 2798–2803.

- [17] Y. Lo, C. Ho, y J. Wang, "Elimination of the output voltage imbalance in a half-bridge boost rectifier," *IEEE Transactions on Power Electronics*, vol. 22, no. 4, pp. 1352–1360, July 2007.

- [18] A. Suzdalenko y A. Chub, "Current sensorless control for halfbridge based ac/dc pfc converter with consideration of conduction losses," *International Journal of Circuit Theory and Applications*, vol. 44, pp. 2072 2084, 12 2016.

- [19] H. Youn, J. Park, K. Park, J. Baek, y G. Moon, "A digital predictive peak current control for power factor correction with lowinput current distortion," *IEEE Transactions on Power Electronics*, vol. 31, no. 1, pp. 900–912, Jan 2016.

- [20] H. S. Nair y N. Lakshminarasamma, "Predictive average current control considering non-idealities for a

- boost pfc converter," in 2018 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Dec 2018, pp. 1–6.

- [21] T. Xue y H. Cheng, "Research and improvement of current hysteresis control strategy for boost dc-dc converter," in 2018 International Conference on Sensor Networks and Signal Processing (SNSP), Oct 2018, pp. 266–270.

- [22] S. Parui y B. Basak, "Evolution of new types of borderline trajectories in state space in current mode controlled dc-dc converter due to switching delay," in *Proceedings of The 2014 International Conference on Control, Instrumentation, Energy and Communication (CIEC)*, Jan 2014, pp. 275–280.

- [23] Y. Liang, Z. Liang, D. Zhao, Y. Huangfu, L. Guo, y B. Zhao, "Model predictive control of interleaved dc-dc boost converter with current compensation," in *2019 IEEE International Conference on Industrial Technology (ICIT)*, Feb 2019, pp. 1701–1706.

- [24] Yeong-Jun Choi, Rae-Young Kim, y Tae-Jin Kim, "A novel active discontinuous pwm control strategy for high efficiency partial switching predictive current-mode control pfc converter," in 2017 *IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017 ECCE Asia)*, June 2017, pp. 236–241.

- [25] L. Rosseto, G. Spiazzi, y P. Tenti, "Control techniques for power factor correction convertersl," pp. 1-9, 1994.

- [26] J. Bayona, H. Chamorro, A. Sánchez, J. Aguillón García, y D. Rubio, "Linear control of a power factor correction rectifier in half-bridge configuration," *IEEE CACIDI 2016 IEEE Conference on Computer Sciences*, pp. 1 6, 2016.

- [27] V. Blasko y V. Kaura, "A novel control to actively damp resonance in input lc filter of a three-phase voltage source converter," *IEEE Transactions on Industry Applications*, vol. 33, no. 2, pp. 542–550, March 1997.

- [28] C.-T. Chen, Analog y Digital Control System Design: TransferFunction, State-Space, and Algebraic Methods. Oxford University Press, 2006.

- [29] MathWorks. (2009) PID controller types for tuning. Documentation. MathWorks MATLAB y Simulink. [En línea]. Disponible en: https://www.mathworks.com/help/control/ug/ pid-controller-types-for-tuning.html

[30] MathWorks. (2009) PID controller, discrete PID controller. Documentation. MathWorks - MATLAB y Simulink. Recuperado el día 10 de enero de 2017. [En línea]. Disponible en: https://www.mathworks.com/help/simulink/slref/pidcontroller.html