Revista Politécnica

ISSN: 1390-0129

ISSN: 2477-8990

Escuela Politécnica Nacional

Acurio, Eliana; Trojman, Lionel; De-Jaeger, Brice; Bakeroot, Benoit

Estudio de Confiabilidad en Diodos Basados en AlGaN/GaN Durante el Estado de Encendido

Revista Politécnica, vol. 50, núm. 1, 2022, Agosto-Octubre, pp. 27-34

Escuela Politécnica Nacional

DOI: <https://doi.org/10.33333/rp.vol50n1.03>

Disponible en: <https://www.redalyc.org/articulo.oa?id=688772225003>

- ▶ Cómo citar el artículo

- ▶ Número completo

- ▶ Más información del artículo

- ▶ Página de la revista en redalyc.org

Sistema de Información Científica Redalyc

Red de Revistas Científicas de América Latina y el Caribe, España y Portugal

Proyecto académico sin fines de lucro, desarrollado bajo la iniciativa de acceso abierto

# Estudio de Confiabilidad en Diodos Basados en AlGaN/GaN Durante el Estado de Encendido

Acurio, Eliana<sup>1, 2,\*</sup> ; Trojman, Lionel<sup>2, 3</sup> ; De Jaeger, Brice<sup>4</sup> ; Bakeroot, Benoit<sup>4, 5</sup>

<sup>1</sup>*Escuela Politécnica Nacional, Departamento de Física, Quito, Ecuador*

<sup>2</sup>*Universidad San Francisco de Quito, IMNE, Quito, Ecuador*

<sup>3</sup>*Instituto de Electrónica de París ISEP, LISITE, París, Francia*

<sup>4</sup>*imec, Lovaina, Bélgica*

<sup>5</sup>*Universidad de Gante, Gante, Bélgica*

**Resumen:** Este trabajo tiene como objetivo estudiar la degradación de los diodos de barrera Schottky (SBD) con una terminación de borde cerrado (GET) bajo condiciones de estrés en estado de encendido en tecnologías de 200V y 650V. Después de todos los experimentos de estrés, se observa un comportamiento recuperable, que indica el atrapamiento de cargas en defectos preexistentes y no creación de nuevas trampas. Un análisis estadístico amplio demuestra una mayor confiabilidad y una vida útil más larga en comparación con trabajos anteriores en una tecnología de 200 V. Para la tecnología de 650V, se analizaron variaciones en el ánodo como una doble capa GET y el uso de Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> como dieléctrico. Se obtuvo una menor degradación total en el segundo caso gracias a la compensación entre los mecanismos de resistencia de encendido (R<sub>ON</sub>) y voltaje de encendido (V<sub>TON</sub>). Se observan algunas diferencias sistemáticas en la degradación de los parámetros según la ubicación de la oblea, probablemente causadas por variaciones relacionadas con el proceso. Mediante el uso de la técnica de pares coincidentes (MP), se ha demostrado que se pueden obtener distribuciones de probabilidad caracterizadas por pendientes de Weibull únicas sobre la oblea que podrían permitir una mejor caracterización de la confiabilidad intrínseca de estos dispositivos.

**Palabras clave:** AlGaN/GaN, barrera Schottky, confiabilidad, diodos, intrínseco.

## Reliability Study on Diodes Based on AlGaN/GaN During the On State

**Abstract:** This work aims to study the degradation of Schottky Barrier Diodes (SBD) with a gated edge termination (GET) under On-state stress conditions in 200V and 650V technologies. After all the stress experiments, a recoverable behavior is observed, which indicates the trapping of charges in pre-existing defects and no creation of new traps. An extensive statistical analysis demonstrates higher reliability and longer lifetime compared to previous work on 200V technology. For 650V technology, variations in the anode as a double layer GET and the use of Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> as dielectric were analyzed. Less total degradation was obtained in the second case thanks to compensation between the on-resistance (R<sub>ON</sub>) and the turn-on voltage (V<sub>TON</sub>) mechanisms. There are some systematic differences in the degradation of the parameters according to the location of the wafer, probably caused by variations related to the process. By using the matched pairs (MP) technique, it has been shown that probability distributions characterized by unique Weibull slopes on the wafer can be obtained and this could allow a better characterization of the intrinsic reliability of these devices.

**Keywords:** AlGaN/GaN, Schottky barrier, diodes, intrinsic, reliability.

### 1. INTRODUCCIÓN

Los dispositivos basados en Nitruro de Galio (GaN) son cada vez más atractivos en la electrónica de potencia ya que en combinación con el Nitruro de Aluminio y Galio (AlGaN) pueden formar heteroestructuras con un canal bidimensional de gas de electrones (2 DEG) evitando procesos de dopaje y aumentando la movilidad en el canal (Morkoç et al., 1994). Sin

embargo, hay requisitos necesarios que debe cumplir una nueva tecnología de semiconductores para su amplia adopción en los sistemas de conversión de energía.

El primero es la eficiencia, y GaN ha demostrado una completa superioridad sobre el silicio (Si) debido a sus notables características electrónicas, lo que resulta en dispositivos de rápida conmutación que permiten el diseño de convertidores

\*eliana.acurio@epn.edu.ec

Recibido: 01/12/2020

Aceptado: 12/04/2022

Publicado en línea: 25/05/2022

10.33333/rp.vol50n1.03

CC 4.0

de alta eficiencia con baja pérdida de potencia (Alatawi, et al., 2018), (Hughes et al., 2011), (Wu et al., 2008).

El segundo es la rentabilidad. Si bien la comparación directa de costos entre las tecnologías de semiconductores es complicada debido a todos los elementos que influyen en el costo final (crecimiento epitaxial, fabricación de obleas y ensamblaje), podemos mencionar que uno de los inconvenientes de los dispositivos basados en esta tecnología es el costoso crecimiento homoepitaxial sobre sustratos de GaN. Por lo tanto, se han utilizado obleas más asequibles basadas en sustratos de silicio (GaN-on-Si) para hacerlo más competitivo en los rangos de bajo voltaje (~ 600V), pero esto hace que el dispositivo sea más vulnerable a la creación de defectos debido a la diferencia en los coeficientes de expansión térmica y al desajuste en la red (lattice) de ambos materiales (Marcon et al., 2015; Cheng et al., 2016).

El último requisito es la confiabilidad a largo plazo, es decir, la probabilidad de que el dispositivo opere correctamente en condiciones normales de funcionamiento para la vida útil prevista (Hartzell et al., 2011). La complejidad de los estudios de confiabilidad radica en que el rendimiento del dispositivo es altamente dependiente de los pasos de fabricación, el crecimiento epitaxial, las técnicas de caracterización y la variabilidad entre dispositivo y dispositivo, lo que dificulta tener una comprensión completa de los fenómenos de degradación y un consenso sobre la física detrás de los mecanismos de falla. De forma particular, los diodos de potencia basados en GaN requieren altos voltajes de ruptura ( $V_{BD}$ ) en combinación con valores bajos de voltaje de encendido ( $V_{TON}$ ), resistencia de encendido específica ( $R_{ON,sp}$ ) y corrientes de fuga para reducir las pérdidas de energía y problemas potenciales de confiabilidad.

En los últimos años, se han intentado varios enfoques de procesamiento para mejorar el rendimiento del rectificador/diodo GaN-on-Si. Por ejemplo, se han adoptado estructuras usando placas de campo (field plates) simples y múltiples para aumentar el voltaje de ruptura en los diodos de barrera Schottky (SBD) y para evitar una ruptura prematura (Horii et al., 2009). Para disminuir las corrientes de fuga, se ha demostrado que el máximo campo eléctrico ubicado en la esquina del contacto de Schottky (zona del ánodo) se reduce al introducir una capa de  $\text{Si}_3\text{N}_4$  para crear una terminación de borde cerrado (gated edge termination-GET) (Lenci et al., 2013).

Estudios recientes bajo estrés en estado de apagado en esta estructura han demostrado una falla relacionada a la concentración del campo eléctrico en áreas críticas como la esquina del dieléctrico que forma el GET y el borde del contacto Schottky. Se han obtenido mejoras de confiabilidad debido a una mejor distribución del campo eléctrico utilizando una capa de pasivación más delgada, una segunda capa GET, un mejor proceso de limpieza previo a la deposición en la región del contacto Schottky y una capa de cobertura de  $\text{Si}_3\text{N}_4$  (Acurio et al., 2018; Acurio et al., 2019).

Si bien, los diodos de barrera Schottky con terminación de borde cerrado (GET-SBDs) han demostrado una buena confiabilidad del dispositivo bajo estrés en estado de

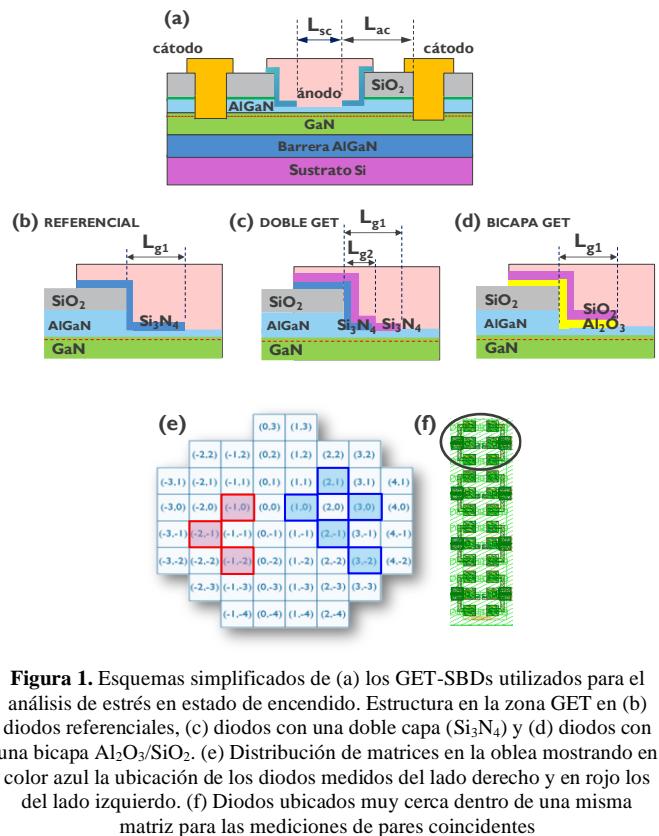

**Figura 1.** Esquemas simplificados de (a) los GET-SBDs utilizados para el análisis de estrés en estado de encendido. Estructura en la zona GET en (b) diodos referenciales, (c) diodos con una doble capa ( $\text{Si}_3\text{N}_4$ ) y (d) diodos con una bicapa  $\text{Al}_2\text{O}_3/\text{SiO}_2$ . (e) Distribución de matrices en la oblea mostrando en color azul la ubicación de los diodos medidos del lado derecho y en rojo los del lado izquierdo. (f) Diodos ubicados muy cerca dentro de una misma matriz para las mediciones de pares coincidentes

encendido utilizando diferentes condiciones y considerando una variedad de geometrías (Tallarico, Stoffels, et al., 2016), (Tallarico, Magnone, et al., 2016), la renovada estructura de GET-SBD, que permitió la mejora mencionada anteriormente en condiciones de estado de apagado (Acurio et al., 2018), aún no se ha verificado bajo estrés en estado de encendido. Por lo tanto, la relevancia de este trabajo radica en predecir correctamente la vida útil de GET-SBDs fabricados en una plataforma tecnológica GaN-on-Si de 200V y 650V. También, en este estudio se busca demostrar que los GET-SBDs exhiben variaciones lo suficientemente bajas para realizar un análisis estadístico y extraer un componente intrínseco que no varía mucho con la ubicación sobre la oblea, lo que permitirá futuros estudios de confiabilidad intrínseca.

El resto del artículo está organizado de la siguiente manera: en la sección 2, proporcionamos los detalles de los dispositivos bajo prueba (DUT); en la sección 3 se explica la metodología de caracterización; en la Sección 4, presentamos y discutimos los resultados del análisis experimental; finalmente, en la Sección 5 se resumen los principales logros de este trabajo.

## 2. FABRICACIÓN DE LOS DISPOSITIVOS

La estructura simplificada de los diodos AlGaN/GaN estudiados en este artículo se muestra en la Figura 1 (a). La estructura epitaxial de la oblea de 200 mm de diámetro se hace crecer sobre un sustrato de Silicio por medio de deposición de vapor químico orgánico metálico (MOCVD). Cuenta con un sustrato diseñado para dos diferentes tecnologías, 200V y 650V. Los dispositivos tienen un canal de GaN de 300 nm de espesor, un espaciador de AlN de 0,5 nm de espesor, una barrera de  $\text{Al}_{0,25}\text{Ga}_{0,75}\text{N}$  de 10 nm de espesor, y una fina capa

de  $\text{Si}_3\text{N}_4$  de 5 nm de espesor. A continuación, el sustrato se pasa a una capa de  $\text{SiO}_2$  y en la región del ánodo, esta capa de pasivación es removida para dar paso al proceso de grabado (etching) que reduce la barrera aproximadamente 6 nm. La estructura GET en las obleas referenciales de ambas tecnologías se obtiene depositando una capa de  $\text{Si}_3\text{N}_4$  de 45 nm de espesor mediante deposición de capa atómica potenciada por plasma (PEALD) con una posterior apertura por grabado en la región central con una longitud  $L_{\text{sc}} = 5 \mu\text{m}$ , lo que da como resultado una longitud de terminación de  $L_{\text{gl}} = 1 \mu\text{m}$  y una distancia ánodo-cátodo de  $L_{\text{ac}} = 6 \mu\text{m}$  en la tecnología de 200 V y de  $L_{\text{gl}} = 2 \mu\text{m}$  y  $L_{\text{ac}} = 16 \mu\text{m}$  en la tecnología de 650 V (ver Figura 1 (b)). A continuación, se deposita y se graba metal a base de TiN sin Au para formar el contacto Schottky en la región del ánodo. Finalmente, los contactos óhmicos se fabrican utilizando una estructura de metal a base de Ti/Al. En el caso de la tecnología de 650 V, se tiene dos obleas adicionales con modificaciones en la zona GET. La primera variación es la deposición y grabación de una capa adicional de  $\text{Si}_3\text{N}_4$  antes de la capa GET principal (ver Figura 1 (c)). En la segunda variación, se deposita una capa interfacial (IL) de 2,5 nm de espesor de  $\text{Al}_2\text{O}_3$  seguida de una capa de  $\text{SiO}_2$  de 35 nm de espesor (ver Figura 1 (d)).

### 3. METODOLOGÍA DE CARACTERIZACIÓN

Las curvas IV de varios diodos en diferentes ubicaciones de las obleas demostraron un excelente desempeño en la caracterización de corriente continua (CC) a  $150^\circ\text{C}$  que es la temperatura usada para acelerar la degradación y considerar el peor de los escenarios para los dispositivos. La Tabla 1 resume los valores medios del voltaje de encendido  $V_{\text{TON}}$  (voltaje ánodo-cátodo  $V_{\text{ac}}$  extraído a 1 mA/mm), el voltaje directo  $V_F$  ( $V_{\text{ac}}$  a 100 mA/mm) y la resistencia de encendido  $R_{\text{ON}}$  que es la máxima pendiente de la curva IV.

Tabla 1. Valores medios de los parámetros de caracterización CC

| Tecnología | Oblea                                                       | $V_{\text{TON}}$ | $V_F$  | $R_{\text{ON}}$ |

|------------|-------------------------------------------------------------|------------------|--------|-----------------|

| 200V       | Referencial ( $\text{Si}_3\text{N}_4$ )                     | 0,53 V           | 1,32 V | 3,84 ohm.mm     |

|            | Referencial ( $\text{Si}_3\text{N}_4$ )                     | 0,60 V           | 1,83 V | 9,02 ohm.mm     |

| 600V       | Doble GET ( $\text{Si}_3\text{N}_4+\text{Si}_3\text{N}_4$ ) | 0,56 V           | 1,98 V | 10,41 ohm.mm    |

|            | Bicapa GET ( $\text{Al}_2\text{O}_3/\text{SiO}_2$ )         | 0,61 V           | 1,74 V | 8,67 ohm.mm     |

El estrés durante el estado de encendido se realizó con el analizador de parámetros Keithley 4200-SCS manteniendo el sustrato y el ánodo conectados a tierra mientras se aplicaba un voltaje negativo entre -4V y -7V en los cátodos durante 1000 s., con lo cual se obtiene un voltaje ánodo-cátodo de estrés positivo. Con el fin de monitorear la evolución de la degradación inducida por el estrés, las mediciones se interrumpieron a intervalos de tiempo fijos utilizando la técnica de medir-estresar-medir (MSM). Después de cada interrupción, se adquirió una curva I-V y se comparó con la curva de referencia medida al comienzo de la prueba para calcular el cambio de voltaje umbral  $\Delta V_{\text{TON}}$ . Cabe señalar que se midieron un total de 64 GET-SBD con un ancho de  $W = 100 \mu\text{m}$  por cada oblea. Los experimentos se realizaron en grupos de diodos ubicados en el lado derecho e izquierdo de las obleas (separados 35 mm del centro de la oblea en

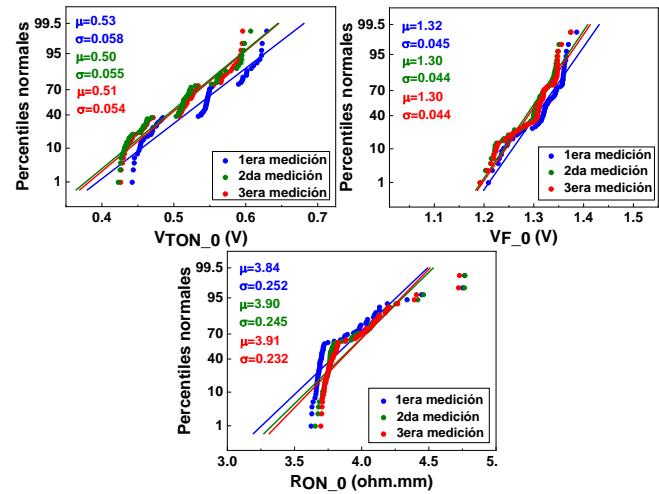

Figura 2. Parámetros iniciales  $V_{\text{TON}}_0$ ,  $V_F_0$  y  $R_{\text{ON}}_0$  medidos al comienzo de tres experimentos bajo las mismas condiciones de estrés ( $V_{\text{estrés}} = 6 \text{ V}$ ,  $T = 150^\circ\text{C}$ ) en la oblea referencial de 200 V. Se obtiene una curva IV repetible en los GET-SBDs solo después de la primera prueba de estrés, la cual se considera una fase inicial de liberación de cargas. Adaptado de (Acurio et al., 2020)

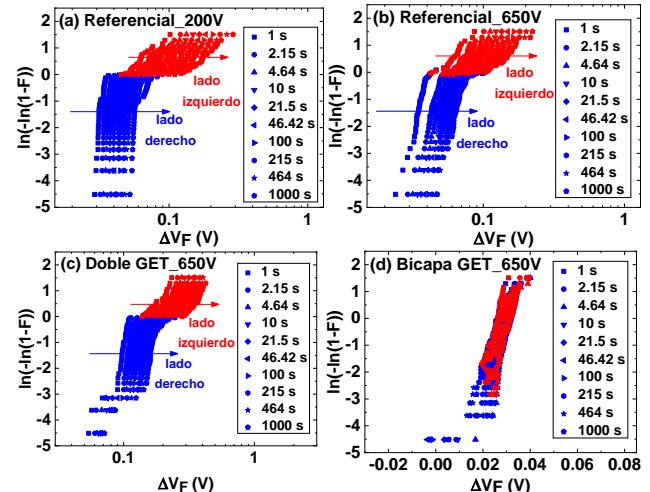

Figura 3. Degradación  $\Delta V_F$  bajo  $V_{\text{estrés}}=6\text{V}$  a  $150^\circ\text{C}$ . Se observa un comportamiento bimodal en los gráficos de Weibull, que muestra la dependencia de la degradación en la ubicación de la oblea, excepto en los dispositivos con una bicapa GET

promedio) para verificar la diferencia de degradación. Para recuperar las curvas iniciales una vez realizada la fase de estrés en todos los dispositivos, se han probado diferentes períodos de tiempo y altas temperaturas ( $150^\circ\text{C}$ ,  $200^\circ\text{C}$  y  $300^\circ\text{C}$ ) (no se muestran los resultados por brevedad). Sin embargo, solo se obtuvo una recuperación completa sometiendo la oblea a un tratamiento térmico a  $300^\circ\text{C}$  durante al menos 30000 s (alrededor de 8 horas) para acelerar la liberación de cargas.

Se llevó a cabo también un análisis de repetibilidad en las obleas aplicando las mismas condiciones de estrés tres veces. Los resultados muestran que los parámetros iniciales  $V_{\text{TON}}_0$ ,  $V_F_0$  y  $R_{\text{ON}}_0$  (parámetros extraídos de la curva IV inicial antes de que se ejecute la prueba de estrés) se vuelven repetibles justo después de la primera prueba de estrés seguida por el tratamiento térmico como se ilustra en la Figura 2 para la oblea de la tecnología de 200V. El mismo comportamiento se observa también en el resto de obleas. Por lo tanto, la primera

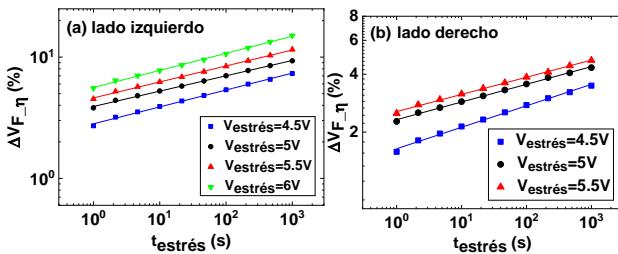

**Figura 4.** Degradación de  $V_F$  bajo diferentes voltajes de estrés usando el parámetro de escala ( $\eta$ ) extraído de las distribuciones de Weibull de los dispositivos en el lado izquierdo (a) y derecho (b) de la oblea referencial en la tecnología de 200V. El mismo procedimiento se ha usado en las obleas referencial, doble GET y bicapa GET en la tecnología de 650V. Adaptado de (Acurio et al., 2020)

prueba de esfuerzo actúa como una fase inicial de eliminación de trampas donde el dispositivo virgen se estabiliza liberando las cargas contenidas originalmente en los centros de captura (Acurio et al., 2017).

## 4. RESULTADOS Y DISCUSIÓN

### 4.1 Análisis estadístico para la predicción de vida útil

Al analizar la degradación después de diferentes períodos de estrés, se encuentra que una distribución de Weibull caracterizada por una función acumulativa igual a  $F(t) = 1 - \exp[-(t/\eta)^\beta]$ , donde  $\eta$  y  $\beta$  son el parámetro de escala y forma, respectivamente, describe mejor los datos de degradación de  $\Delta V_F$  como se muestra en la Figura 3. Se observa claramente un comportamiento bimodal de las mediciones a lo largo de las obleas, excepto en la oblea con una bicapa GET, lo cual será explicado más adelante. Los diodos ubicados en el lado derecho de la oblea se degradan de manera diferente a los dispositivos en el lado izquierdo en las mismas condiciones. Esto demuestra el impacto de la variación extrínseca cuando se aplica un fuerte voltaje de estrés (de 4V a 7V) que supera ampliamente los voltajes normales de operación de los dispositivos (Tabla 1).

Una distribución  $\Delta V_F$  más estrecha se observa en los GET-SBDs ubicados en el lado derecho, lo que demuestra una mejor confiabilidad bajo condiciones de estrés en estado de encendido en comparación con los dispositivos en el lado izquierdo. Aunque el origen de la diferencia en la degradación puede ser de diversa naturaleza, podría atribuirse, por ejemplo, a cambios de espesor en las capas con centros de captura de cargas identificadas del dispositivo, como la barrera AlGaN (Tallarico, Stoffels, et al., 2016) y el dieléctrico GET. Sin embargo, todavía es necesario realizar más investigaciones para comprender mejor este fenómeno.

Una vez separados los datos de las dos distribuciones para cada condición de estrés, se obtiene el parámetro de escala (o valor característico) de cada distribución de Weibull para caracterizar con un único valor la degradación de la población de dispositivos correspondiente. Luego, estos resultados se grafican en función del tiempo de estrés ( $t_{estrés}$ ) y se ajustan linealmente en una escala logarítmica como se muestra en la Figura 4 para determinar cuándo  $\Delta V_F$  alcanza el 5%, que es el criterio de falla adoptado en este trabajo. Cabe destacar que para la estimación de vida útil se ha considerado  $\Delta V_F$  ya que

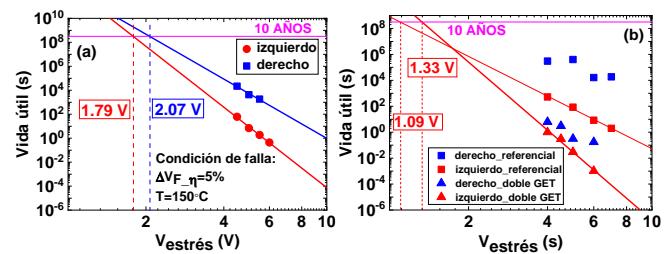

**Figura 5.** Extrapolación del tiempo de vida útil para los dispositivos del lado izquierdo y derecho de (a) la oblea referencial de 200V y (b) las obleas referencial y doble GET de la tecnología de 650V

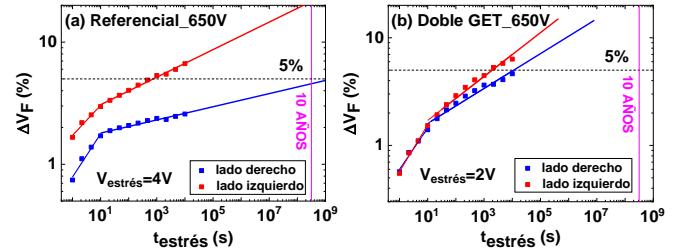

**Figura 6.** Extrapolación del tiempo de vida útil usando menores voltajes de estrés y tiempo más prolongado para los dispositivos del lado izquierdo y derecho de (a) la oblea referencial y (b) la oblea con doble GET de la tecnología de 650V

este parámetro considera tanto la degradación de  $V_{TON}$  como de  $R_{ON}$  a través de la expresión:

$$\Delta V_F = \Delta V_{TON} + (\Delta R_{ON} * I_{AC}) \quad (1)$$

La Figura 5 (a) ilustra la vida útil extrapolada de los GET-SBDs fabricados con la tecnología de 200 V, donde 1,79 V y 2,07 V son el voltaje máximo aplicable a los dispositivos del lado derecho e izquierdo, respectivamente, para tener una degradación de  $V_F$  del 5% en diez años. Para estos dispositivos, el voltaje directo nominal es de 1,32 V. Por lo tanto, la vida útil esperada es incluso superior a 10 años para todos los dispositivos de esta oblea, aunque se degraden de manera diferente. Esto demuestra que los esfuerzos para mejorar la confiabilidad en condiciones de estado apagado en esta tecnología (Acurio et al., 2018) no afectan el funcionamiento en estado encendido e incluso mejoran la vida útil esperada de estos dispositivos.

Para el caso de la oblea referencial en la tecnología de 650V, no se alcanza el tiempo de vida esperado usando las tres condiciones de voltaje y la ley de potencia tanto en el lado derecho como izquierdo de la oblea como se ilustra en la Figura 5 (b). Esto se debe a que, al aumentar el voltaje de estrés, la extrapolación de la vida útil es menos dependiente de este parámetro y se empieza a observar que los valores extraídos tienden a un comportamiento más horizontal con el  $V_{estrés}$ , esto es más notorio en el lado derecho de la oblea referencial (cuadrados azules), por lo que no se ha incluido la curva de ajuste. Sin embargo, usando voltajes menores y tiempos más prolongados de estrés (10000 s) es posible alcanzar una vida útil de 10 años, pero solo con los dispositivos en el lado derecho de la oblea como se muestra en la Figura 6 (a).

Al analizar el impacto en el tiempo estimado de vida cuando se modifica la estructura del ánodo en la tecnología de 650V cambiando desde una capa simple de  $\text{Si}_3\text{N}_4$  (oblea referencial) en la estructura GET a una capa adicional de  $\text{Si}_3\text{N}_4$ , las mediciones indican que la confiabilidad se ve comprometida al aumentar la capa adicional de  $\text{Si}_3\text{N}_4$ . El tiempo en el que se alcanza el criterio de falla disminuye significativamente con respecto a la oblea referencial como se observa en la Figura 5 (b). Aunque la extrapolación para los diodos del lado izquierdo muestre un mejor resultado de la vida útil esperada para la doble capa GET, se debe considerar que la oblea referencial posee una menor dependencia del voltaje de estrés que le imposibilita mejorar el resultado en la extrapolación como se ha mencionado previamente. La Figura 6 (a) y (b) permiten observar una comparación más justa de las dos obleas analizando la degradación de  $V_F$  con valores de estrés más bajos y por lo tanto más próximos a los voltajes normales de operación. En esta comparación, se muestra una mayor degradación de la oblea con doble GET incluso cuando se usa voltaje de estrés menor al usado con la oblea referencial. Esto puede deberse a que el atrapamiento de cargas es más severo ya que los diodos poseen una capa adicional de dieléctrico en donde probablemente los centros de captura son mayores que con una sola capa.

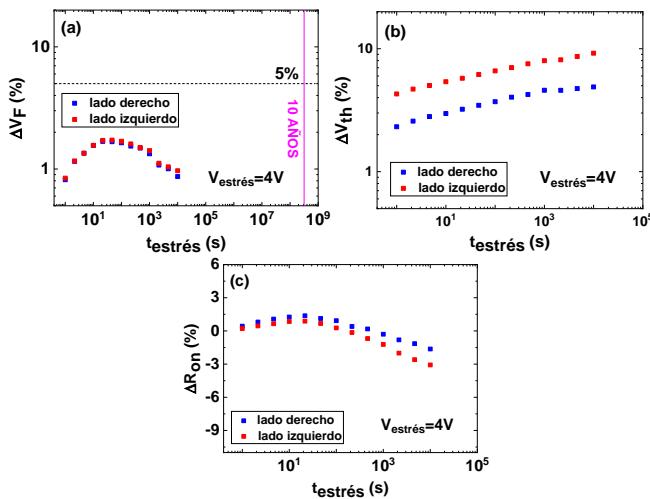

En el caso de la oblea con una bicapa de  $\text{Al}_2\text{O}_3/\text{SiO}_2$ , el tiempo de vida no ha podido ser extrapolado ya que la degradación de  $V_F$  presenta un comportamiento inusual. Al comienzo del estrés,  $V_F$  se degrada de manera normal. Sin embargo, a medida que aumenta el tiempo, este parámetro empieza a recuperarse indicando un punto de inversión. Esto imposibilita llegar al criterio de falla de 5% de desplazamiento en  $V_F$  y extrapolar el tiempo de vida útil usando la ley de potencia. Al analizar individualmente los componentes de  $V_F$  ( $R_{ON}$  y  $V_{TON}$ ) se identifica que este comportamiento se debe a una recuperación de  $R_{ON}$  durante el estrés, mientras que  $V_{TON}$  continúa degradándose de manera habitual como se muestra en la Figura 7. El estudio de este punto de inversión está fuera del alcance de este trabajo, pero va a ser considerado para futuras investigaciones.

**Figura 7.** Degradación de los parámetros (a)  $V_F$ , (b)  $V_{TON}$  y (c)  $R_{ON}$  en los dispositivos del lado derecho e izquierdo de la oblea con bicapa GET en la tecnología de 650V. Se observa un punto de inversión en  $\Delta V_F$  debido a una recuperación en el comportamiento de  $R_{ON}$ .

#### 4.2 Extracción de la degradación intrínseca de $V_{TON}$

Como se ilustra en la Figura 2, el voltaje de encendido inicial  $V_{TON\_0}$ , que se extrajo de la curva I-V inicial antes de los experimentos de estrés, no muestra una distribución de probabilidad clara. Las distribuciones más comunes, la normal (ver Figura 2) y la Weibull (no mostrada), se utilizaron para ajustar los datos. Sin embargo, la agrupación de diodos ubicados en posiciones cercanas indica una variación de procesamiento extrínseco a través de las obleas, lo que sugiere un componente extrínseco en  $V_{TON}$ . Como resultado,  $V_{TON}$  se puede expresar mediante la siguiente relación:

$$V_{TON}(t_{stress}) = \Phi_{MS} + 2\Phi_F + \frac{Q_{OT}}{C_{OX}} + V_{TON\_ext} \quad (2)$$

donde  $\Phi_{MS}$  es la diferencia de la función de trabajo del semiconductor de metal,  $2\Phi_F$  es el potencial de superficie,  $Q_{OT}$  es la densidad de defectos de carga en el óxido/dieléctrico,  $C_{OX}$  es la capacitancia del óxido y  $V_{TON\_ext}$  es el componente extrínseco. La degradación de  $V_{TON}$  inducida por el estrés puede ser dada por:

$$\Delta V_{TON}(t_{stress}) \approx \frac{\Delta Q_{OT}(t_{stress})}{C_{OX}} + V_{TON\_ext} \quad (3)$$

El componente extrínseco se debe típicamente a variaciones relacionadas con el proceso, por ejemplo, por diferencias en los espesores de las capas o variaciones de estequiométrica del material a través de la oblea. Por lo tanto, la diferencia extrínseca entre dos dispositivos ubicados lejos uno del otro en la oblea es relativamente grande, pero esta diferencia debería reducirse mucho en dos dispositivos muy próximos.

Basándonos en el principio de pares coincidentes normalmente utilizados en el tiempo cero y el análisis de variabilidad dependiente del tiempo en tecnologías VLSI de escala profunda (Kaczer et al., 2015), se selecciona pares formados por dispositivos en lado izquierdo (I) y derecho (D) dispuestos muy cercanamente en la misma matriz también conocida como *die* (Figura 1 (f)) para obtener las diferencias de los respectivos parámetros de la siguiente manera:

$$\delta V_{TON\_0} \approx V_{TON\_0,I} - V_{TON\_0,D} \quad (4)$$

$$\delta \Delta V_{TON} \approx \Delta V_{TON,I} - \Delta V_{TON,D} \quad (5)$$

donde  $V_{TON\_ext,I} = V_{TON\_ext,D}$  y consecuentemente la Ecuación (3) se puede simplificar a la siguiente expresión:

$$\delta \Delta V_{TON}(t_{stress}) \approx \frac{\delta \Delta Q_{OT}(t_{stress})}{C_{OX}} \quad (6)$$

que representa la variación intrínseca de  $\Delta V_{TON}$  y donde no hay impacto del componente extrínseco. Por tanto, la degradación inducida por el estrés está directamente relacionada con el número de cargas atrapadas durante el estrés.

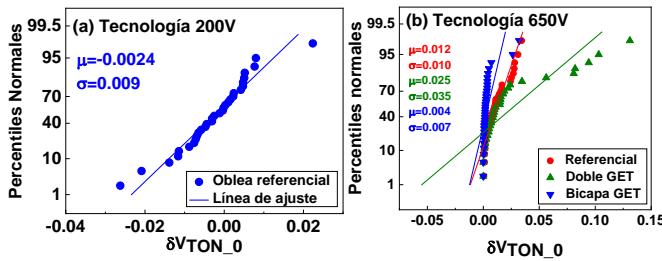

La Figura 8 muestra las distribuciones de probabilidad (normal) del cambio diferencial  $\delta V_{TON\_0}$ , que indica claramente una mejor uniformidad en comparación con la distribución  $V_{TON\_0}$  de diodos individuales en todas las obleas.

**Figura 8.** Distribución normal del cambio diferencial  $\delta V_{TON\_0}$  en (a) la tecnología de 200V y (b) 650V, respectivamente. Una vez que se elimina el componente extrínseco (sistemático), los datos pueden adaptarse mejor a las líneas de ajuste

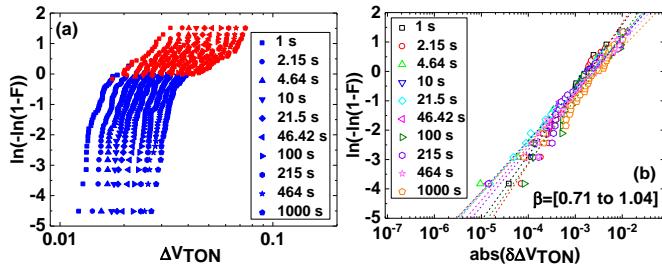

**Figura 9.** (a) Distribución de  $\Delta V_{TON}$  para diferentes períodos de estrés (se observa dependencia en la ubicación de la oblea). (b) Distribución de Weibull del cambio diferencial  $\delta \Delta V_{TON}$  para diferentes períodos de estrés en la oblea referencial de la tecnología de 200V cuando se aplica  $V_{estrés}=6V$  y  $T=150^{\circ}C$ . Tomado de (Acurio et al., 2020)

Con esta métrica de pares coincidente la oblea con una doble GET, muestra mayor variabilidad con respecto a la oblea referencial en la tecnología de 650V como se muestra en la Figura 8 (b). Esto indica mayor variación en el proceso de fabricación, es decir, la deposición de la capa adicional no es uniforme en todos los dispositivos.

Por otro lado, la oblea con una bicapa GET, hasta el momento ha demostrado tener mayor uniformidad en el proceso de fabricación con respecto a la oblea referencial y la hace atractiva para futuras mejoras de confiabilidad de diodos Schottky basados en AlGaN/ GaN.

De manera similar al análisis de  $V_{TON\_0}$ , el concepto de pares coincidentes también se puede extender a las mediciones de  $\Delta V_{TON}$  siguiendo la Ecuación (5). El comportamiento bimodal que caracteriza a cada lado de la oblea desaparece convergiendo en una sola pendiente de Weibull para cada período de estrés que casi se superponen entre sí. En la Figura 9, se demuestra este comportamiento tomando como ejemplo la oblea referencial en la tecnología de 200V. Los valores bajos de  $\beta$  de las distribuciones  $\delta \Delta V_{TON}$  podrían estar relacionados con una mayor variación inducida por la reducción de las muestras en la técnica de pares coincidentes. Sin embargo, la ventaja de esta técnica para extraer distribuciones de Weibull sin la influencia de cambios de espesor u otras variaciones relacionadas con el proceso se puede utilizar para futuros estudios de confiabilidad intrínseca que permitan comparaciones directas entre nuevas arquitecturas y materiales en la región GET.

## 5. CONCLUSIONES

En este trabajo, hemos analizado la degradación de diodos Schottky basados en AlGaN/GaN bajo condiciones de estrés en estado de encendido. Observamos un comportamiento recuperable para todos los voltajes de estrés aplicados, lo que indica que el proceso de atrapamiento de cargas ocurre mayormente en defectos preexistentes. Los dispositivos se degradan de manera diferente dependiendo de la ubicación en la oblea debido principalmente a variaciones relacionadas con el proceso. Sin embargo, se demostró mediante el uso de estadísticas más amplias que los diodos actuales de la tecnología de 200 V tienen una mejor confiabilidad en el estado de encendido con una vida útil más prolongada que en trabajos anteriores. Además, con base en la metodología de pares coincidentes, es posible reducir la componente extrínseca y/o sistemática en  $V_{TON\_0}$  y  $\Delta V_{TON}$  para obtener distribuciones de probabilidad con pendientes de Weibull simples y bien definidas. La estructura más prometedora en la tecnología de 650 V considerando esta métrica, es aquella con una bicapa de  $Al_2O_3/SiO_2$  ya que muestra una menor degradación de los parámetros y exhibe mayor uniformidad en el proceso de fabricación en comparación con las otras obleas.

## REFERENCIAS

- Acurio, E., Crupi, F., Magnone, P., Trojman, L., Meneghesso, G., & Iucolano, F. (2017). On recoverable behavior of PBTI in AlGaN/GaN MOS-HEMT. *Solid-State Electronics*, 132, 49–56. <https://doi.org/10.1016/j.sse.2017.03.007>

- Acurio, E., Trojman, L., Crupi, F., Moposita, T., De Jaeger, B., & Decoutere, S. (2020). Reliability Assessment of AlGaN/GaN Schottky Barrier Diodes under ON-state stress. *IEEE Transactions on Device and Materials Reliability*, 20(1):167-171. <https://doi.org/10.1109/TDMR.2020.2969638>

- Acurio, Eliana, Crupi, F., Ronchi, N., De Jaeger, B., Bakeroot, B., Decoutere, S., & Trojman, L. (2018). Reliability Improvements in AlGaN/GaN Schottky Barrier Diodes With a Gated Edge Termination. *IEEE Transactions on Electron Devices*, 65(5), 1765–1770. <https://doi.org/10.1109/TED.2018.2818409>

- Acurio, Eliana, Crupi, F., Ronchi, N., De Jaeger, B., Bakeroot, B., Decoutere, S., & Trojman, L. (2019). Influence of GaN- and Si 3 N 4 - Passivation Layers on the Performance of AlGaN/GaN Diodes With a Gated Edge Termination. *IEEE Transactions on Electron Devices*, 66(2), 883–889. <https://doi.org/10.1109/TED.2018.2888809>

- Alatawi, K., Almasoudi, F., Manandhar, M., Matin, M. (2018). Comparative Analysis of Si- and GaN-Based Single-Phase Transformer-Less PV Grid-Tied Inverter. *Electronics*, 7(3), 34. <https://doi.org/10.3390/electronics7030034>

- Cheng, J., Yang, X., Sang, L., Guo, L., Zhang, J., Wang, J., He, C., Zhang, L., Wang, M., Xu, F., Tang, N., Qin, Z., Wang, X., & Shen, B. (2016). Growth of high quality and uniformity AlGaN/GaN heterostructures on Si substrates using a single AlGaN layer with low Al composition. *Scientific Reports*, 6(1), 23020. <https://doi.org/10.1038/srep23020>

- Hartzell, A. L., da Silva, M. G., & Shea, H. R. (2011). Lifetime Prediction. In *World Wide Web Internet And Web Information Systems* (Vol. 52, pp. 9–42). [https://doi.org/10.1007/978-1-4419-6018-4\\_2](https://doi.org/10.1007/978-1-4419-6018-4_2)

- Horii, T., Miyazaki, T., Saito, Y., Hashimoto, S., Tanabe, T., & Kiyama, M. (2009). High-Breakdown-Voltage GaN Vertical Schottky Barrier Diodes with Field Plate Structure. *Materials Science Forum*, 615–617, 963–966. <https://doi.org/10.4028/www.scientific.net/MSF.615-617.963>

Hughes, B., Yoon, Y. Y., Zehnder, D. M., & Boutros, K. S. (2011). A 95% Efficient Normally-Off GaN-on-Si HEMT Hybrid-IC Boost-Converter with 425-W Output Power at 1 MHz. *2011 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS)*, 1–3. <https://doi.org/10.1109/CSICS.2011.6062460>

Kaczer, B., Franco, J., Roussel, P. J., Groeseneken, G., Chiarella, T., Horiguchi, N., & Grasser, T. (2015). Extraction of the Random Component of Time-Dependent Variability Using Matched Pairs. *IEEE Electron Device Letters*, 36(4), 300–302. <https://doi.org/10.1109/LED.2015.2404293>

Lenci, S., De Jaeger, B., Carbonell, L., Hu, J., Mannaert, G., Wellekens, D., You, S., Bakeroor, B., & Decoutere, S. (2013). Au-Free AlGaN/GaN Power Diode on 8-in Si Substrate With Gated Edge Termination. *IEEE Electron Device Letters*, 34(8), 1035–1037. <https://doi.org/10.1109/LED.2013.2267933>

Marcon, D., Saripalli, Y. N., & Decoutere, S. (2015). 200mm GaN-on-Si epitaxy and e-mode device technology. *2015 IEEE International Electron Devices Meeting (IEDM)*, 2016-Febru, 16.2.1-16.2.4. <https://doi.org/10.1109/IEDM.2015.7409709>

Morkoç, H., Strite, S., Gao, G. B., Lin, M. E., Sverdlov, B., & Burns, M. (1994). Large-band-gap SiC, III-V nitride, and II-VI ZnSe-based semiconductor device technologies. *Journal of Applied Physics*, 76(3), 1363–1398. <https://doi.org/10.1063/1.358463>

Tallarico, A. N., Magnone, P., Stoffels, S., Lenci, S., Hu, J., Marcon, D., Sangiorgi, E., Decoutere, S., & Fiegna, C. (2016). Understanding the degradation sources under ON-state stress in AlGaN/GaN-on-Si SBD: Investigation of the anode-cathode spacing length dependence. *2016 IEEE International Reliability Physics Symposium (IRPS)*, 2016-Sept, 4A-5-1-4A-5-6. <https://doi.org/10.1109/IRPS.2016.7574530>

Tallarico, A. N., Stoffels, S., Magnone, P., Hu, J., Lenci, S., Marcon, D., Sangiorgi, E., Fiegna, C., & Decoutere, S. (2016). Reliability of Au-Free AlGaN/GaN-on-Silicon Schottky Barrier Diodes Under ON-State Stress. *IEEE Transactions on Electron Devices*, 63(2), 723–730. <https://doi.org/10.1109/TED.2015.2507867>

Wu, Y., Jacob-Mitos, M., Moore, M. L., & Heikman, S. (2008). A 97.8% Efficient GaN HEMT Boost Converter With 300-W Output Power at 1 MHz. *IEEE Electron Device Letters*, 29(8), 824–826. <https://doi.org/10.1109/LED.2008.2000921>

## BIOGRAFÍAS

**Eliana Acurio**, recibió el título en Ingeniería en Electrónica y Control de la Escuela Politécnica Nacional, Quito, Ecuador, en 2011. También recibió el título de master en Mecatrónica y Sistemas Micro-Mecatrónicos por la Hochschule Karlsruhe, Karlsruhe, Alemania y la Universidad de Oviedo, Gijón, España en 2014. Obtuvo el Ph.D. en Tecnologías de la Información y Comunicación por la Universidad de la Calabria, Cosenza, Italia, en 2019. Actualmente se desempeña como profesora e investigadora en el Departamento de Física de la Escuela Politécnica Nacional. El enfoque principal de su trabajo es la confiabilidad de los dispositivos basados en GaN para aplicaciones energéticas eficientes.

**Lionel Trojman**, tiene un título en Física por la Universidad de Aix-Marsella, Francia, en 2002, Recibió el título de master en física aplicada a la micro y nanoelectrónica y en ingeniería eléctrica en microelectrónica y telecomunicaciones por la “Ecole Polytechnique Universitaire de Marseille”, Aix-Marseille University, en 2004. Recibió su título de Ph.D. en Ingeniería Eléctrica por KU Leuven en colaboración con imec, Bélgica, en 2009. Desde 2009, se desempeñó como profesor en el departamento de ingeniería eléctrica y electrónica de la USFQ, Ecuador. Actualmente trabaja como profesor para Isep, Francia, desde 2019. Sus intereses de investigación actuales incluyen los fenómenos de transporte para MOSFET ultraescalado (sub-100nm) con dieléctricos UTEOT high-k con arquitecturas convencionales y nuevas (FinFET, FDSOI o TFET) para Tecnologías CMOS, memorias (ReRAM, MTJ) y dispositivos electrónicos de potencia GaN.

**Brice De Jaeger**, recibió su título universitario y de maestría en ingeniería eléctrica de la Universidad de Gante, Gante, Bélgica, en 1994 y 1997, respectivamente. Ha sido ingeniero de investigación en diferentes departamentos en el instituto imec, Lovaina, Bélgica. Ha colaborado en el desarrollo tecnológico, integración y caracterización de interconexiones y transistores CMOS de germanio. Sus intereses de investigación actuales incluyen la tecnología GaN para aplicaciones de energía.

**Benoit Bakeroor**, recibió su título de maestría en Física en 1997 y el Ph.D. en Ingeniería Eléctrica en 2004, ambos en la Universidad de Gante, Bélgica. Desde 1998, Benoit Bakeroor trabaja en imec, donde ha estado involucrado en la investigación de dispositivos de potencia de Si y GaN con un enfoque en simulaciones de tecnología de diseño asistido por computadora (TCAD), modelado compacto, confiabilidad y física de dispositivos. Es autor y coautor de más de 80 artículos en revistas científicas internacionales y actas de congresos. También es profesor asociado a tiempo parcial en la Universidad de Gante.