Ingeniería. Investigación y Tecnología

ISSN: 1405-7743

iit.revista@gmail.com

Universidad Nacional Autónoma de

México

México

Garduza-González, Sergio; Gómez-Castañeda, Felipe; Moreno-Cadenas, José Antonio;

Víctor Hugo, Ponce-Ponce

Prototipo sensor de imagen CMOS con arquitectura de modulación a nivel columna

Ingeniería. Investigación y Tecnología, vol. VXII, núm. 2, abril-junio, 2016, pp. 237-249

Universidad Nacional Autónoma de México

Distrito Federal, México

Disponible en: <http://www.redalyc.org/articulo.oa?id=40445803008>

- ▶ Cómo citar el artículo

- ▶ Número completo

- ▶ Más información del artículo

- ▶ Página de la revista en [redalyc.org](http://redalyc.org)

redalyc.org

Sistema de Información Científica

Red de Revistas Científicas de América Latina, el Caribe, España y Portugal

Proyecto académico sin fines de lucro, desarrollado bajo la iniciativa de acceso abierto

# Prototipo sensor de imagen CMOS con arquitectura de modulación a nivel columna

*A Prototype CMOS Image Sensor with a Column-Level Modulation Architecture*

Garduza-González Sergio

*Instituto Politécnico Nacional, UPIITA*

*Departamento de Ingeniería*

*Correo: sgarduza@ipn.mx*

Gómez-Castañeda Felipe

*Centro de Investigación y de Estudios Avanzados del IPN*

*Departamento de Ingeniería Eléctrica*

*Correo: fgomez@cinvestav.mx*

Moreno-Cadenas José Antonio

*Centro de Investigación y de Estudios Avanzados del IPN*

*Departamento de Ingeniería Eléctrica*

*Correo: jmoreno@cinvestav.mx*

Ponce-Ponce Víctor Hugo

*Instituto Politécnico Nacional, CIC*

*Correo: vponce@cic.ipn.mx*

Información del artículo: recibido: febrero de 2015, reevaluado: abril de 2015, aceptado: agosto de 2015

## Resumen

Un sensor de imagen CMOS se compone de matriz de sensado, lógica de selección fila/columna y convertidor analógico-digital. El desempeño de este último influye en el desempeño global del sensor de imagen. Una alternativa estudiada en los últimos años, es la arquitectura de sobremuestreo, que a diferencia de la tradicional arquitectura Nyquist, alcanza la misma razón señal a ruido, pero con cuantificador de 1-bit. Esta importante ventaja es atractiva para depender menos de las imperfecciones tecnológicas de los circuitos. Este artículo presenta el diseño de un prototipo sensor de imagen CMOS con prestaciones básicas para fotografía digital, que incluye matriz de fotodiodos, circuitos de selección fila/columna y modulador sigma-delta a nivel de 4-columnas. La modulación sigma-delta aprovecha la ventaja del sobremuestreo, disminuye el ruido de cuantificación en banda, es robusto y compatible con dispositivos MOSFET. Para el diseño del modulador se optimizó la razón señal a ruido, a través de un modelo comportamental. Todos los circuitos se implementaron con reglas de diseño de señal mixta y se fabricaron en un solo chip con tecnología CMOS estándar. Los resultados de mediciones e imágenes obtenidas con el prototipo muestran que la metodología de diseño que se utilizó es fiable. Este prototipo es un circuito VLSI y es la base del diseño de nuevos sistemas de detección fotónica para diversas aplicaciones.

## Descriptores:

- convertidor analógico-digital de sobremuestreo

- densidad espectral de potencia

- modelo comportamental

- modulación sigma-delta

- razón señal a ruido de cuantificación

- ruido de cuantificación

- sensor de imagen CMOS

- transistor de efecto de campo de metal-óxido-semiconductor

## Abstract

A CMOS image sensor is composed of array pixel, row/column selection logic and analog to digital converter. The performance of this latter influences the image sensor overall performance. An alternative studied in recent years, is the oversampling architecture, unlike traditional Nyquist architecture, has the same signal to noise ratio, but with 1-bit quantizer. It is major advantage is attractive to reduce dependence on technological imperfections of the circuits. This paper presents the design of a prototype CMOS image sensor with basic performance to digital still-photography, which includes sigma-delta modulator at the 4-columns. The sigma -delta modulation takes advantage of oversampling, robustness and compatibility with MOS-FET devices. To design the modulator, the SNR was optimized, through a model which includes noise sources. All circuits were implemented with mixed signal design rules and manufactured on a single chip using standard CMOS technology. The results of measurements and images obtained with the prototype show that the design methodology used is reliable. This prototype is a VLSI circuit and is the basis for the design of the new photodetection systems in other applications.

## Keywords:

- oversampling analog-digital converter

- power spectral density

- behavioral model

- sigma-delta modulation

- signal-to-quantizer noise-ratio

- quantizer noise

- CMOS image sensor

- metal-oxide-semiconductor field effect transistor

## Introducción

Como resultado del avance en los procesos de fabricación de circuitos integrados, llegó el sensor de imagen basado en silicio. Actualmente existen dos versiones: el dispositivo acoplado por carga o CCD y el sensor de imagen CMOS o CIS (El Gamal y Eltoukhy, 2005).

A mediados de los años 90 surgió el CIS, fabricado en tecnología CMOS estándar, el cual se logró gracias al uso de máscaras. Un CIS es un chip constituido por: matriz de pixeles, decodificador, amplificadores, convertidor analógico-digital (ADC) y circuito de control y temporizado. Tradicionalmente, los diseñadores han implementado el ADC con arquitectura tipo Nyquist (Hwang y Song, 2014), esta arquitectura requiere una razón señal a ruido de cuantificación del orden de 50 dB para alcanzar resoluciones de 8 bits. Dichos ADCs requieren un filtro limitador de ancho de banda, muestrador, cuantificador multinivel y codificador digital. Todo ello convierte a los ADCs tipo Nyquist en sistemas complejos de señal mixta de bajo desempeño, que utilizan espacio considerable en el chip.

Una alternativa a los convertidores tipo Nyquist, que en años recientes se prefiere, es la conversión por sobremuestreo y particularmente, la técnica que usa modulador sigma-delta ( $\Sigma\Delta M$ ). Un  $\Sigma\Delta M$  puede formar parte de un ADC o solamente ser un bloque de sensado. En cualquier caso, la salida de un  $\Sigma\Delta M$  es una versión digital de la señal, que llega a ser de alta resolución, pero con baja velocidad de conversión (De La Rosa, 2011). Debido a esto, los  $\Sigma\Delta M$  son útiles para la digitalización de señales de baja frecuencia. Un  $\Sigma\Delta M$  lleva a cabo dos operaciones: discretización en amplitud y suavizado del ruido de cuantificación (Proakis y Manolakis, 2007), es decir, el desplazamiento de componentes de ruido de cuantificación fuera del ancho de banda de interés. Tratándose de un  $\Sigma\Delta M$  de 1-bit, su salida produce una sucesión de pulsos digitales, en los cuales se encuentra codificada la señal de entrada, similar a la modulación por pulsos codificados o PCM.

Este artículo presenta el diseño de un prototipo sensor de imagen CMOS para fotografía digital elemental. En este prototipo se toma en cuenta el tiempo de exposición, el cual se determina por el tiempo de integración en los pixeles (también llamado *shutter time*). En una cámara fotográfica convencional, el tiempo de integración suele estar entre 30 s y 250  $\mu$ s. Para el prototipo CIS se seleccionó un tiempo de integración máximo de 4 ms. Tomando este tiempo como referencia, realizar la lectura de una matriz de 24x32 pixeles, requeriría un tiempo de lectura por pixel ( $t_l$ ) de aproximadamente 5.2  $\mu$ s

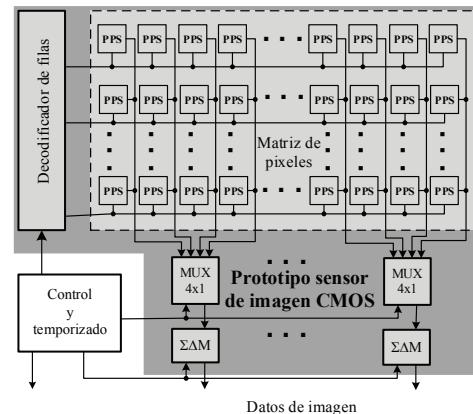

Figura 1. Arquitectura para el prototipo sensor de imagen CMOS

El sistema en chip propuesto se presenta en la figura 1, incluye arreglo de  $24 \times 32$  pixeles tipo PPS, selector de filas, columnas y  $\Sigma\Delta M$  cada 4-columnas. Los circuitos de control y temporizado son externos al chip. Se utilizó modelado comportamental a nivel sistema para la obtención de parámetros de diseño y proponer las dimensiones finales de los MOSFETs. Finalmente, los circuitos se implementaron con reglas de diseño de señal mixta y se fabricaron en un solo chip de  $4 \text{ mm}^2$  con tecnología CMOS estándar pozo-n.

El resto de este artículo se organiza en seis secciones más. La segunda sección muestra las características del foto-detectador. La tercera sección presenta la estimación de la razón señal a ruido de cuantificación (SQNR) del  $\Sigma\Delta M$  de 1er-orden y 1-bit; el objetivo es poner en perspectiva las variables involucradas en el diseño. La cuarta sección presenta el modelo comportamental del modulador y su simulación con herramientas computacionales, con ello identificamos los parámetros que degradan la razón señal a ruido (SNR). La quinta sección presenta el diseño a nivel circuito. La sexta sección presenta la implementación y mediciones del prototipo sensor de imagen CMOS, finalmente, las conclusiones.

### Características del dispositivo foto-detectador

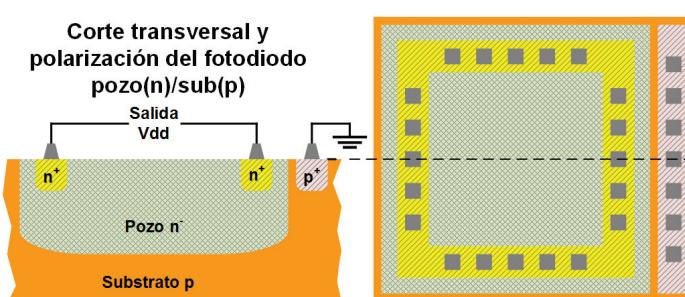

En el prototipo CIS se empleó un fotodiodo pozo-n/substrato-p, para ofrecer mayor factor de llenado en tecnología CMOS estándar, frente a la fotocompuerta y el fototransistor; otra ventaja es su respuesta espectral, centrada entre 600 y 700 nm (Murari *et al.*, 2009). La estructura se muestra en la figura 2. El fotodiodo se polariza en forma inversa para generar una región de carga espacial (SCR) que da origen a un campo eléctrico y una capacitancia. Cuando los fotones inciden sobre el dispositivo, los huecos y electrones generados cercanos a los bordes de la SCR se arrastran hacia las regiones p y n, respectivamente, para así contribuir a la photocurrente. Por otro lado, la capacitancia formada por la unión se utiliza como mecanismo de acumulación de carga.

La tabla 1 resume las características eléctricas del fotodiodo, fabricado en tecnología CMOS estándar. De la

tabla 1 se estima que el intervalo dinámico de la photocurrente es de hasta cuatro órdenes de magnitud, lo que para el modulador representaría una señal de entrada con un intervalo dinámico de 40 dB, suficiente para emplear un  $\Sigma\Delta M$  de 1er-orden.

### Estimación de la SQNR del $\Sigma\Delta M$ de 1er-orden y 1-bit

El desempeño del  $\Sigma\Delta M$  determina el desempeño global del prototipo CIS, de ahí que su diseño deberá tomar en cuenta la mayor cantidad de aspectos físicos de un circuito modulador real. En este contexto, el diseño del  $\Sigma\Delta M$  inicia con la estimación analítica de la razón señal a ruido de cuantificación (SQNR) para una arquitectura ideal. Concretamente, se seleccionó un modulador de 1er-orden y 1-bit en tiempo discreto.

### Estimación analítica

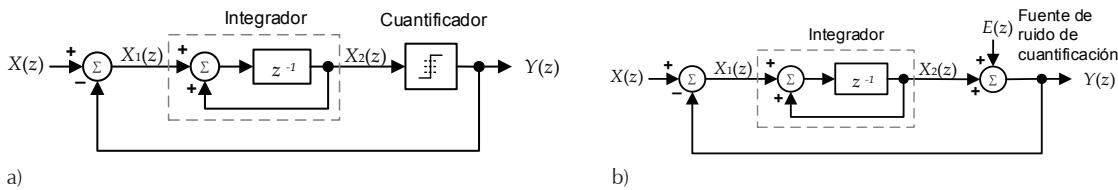

El  $\Sigma\Delta M$  ideal de 1er-orden y 1-bit, en tiempo discreto, se compone de un integrador de 1er-orden, un cuantificador de 1-bit y un lazo de retroalimentación negativa, como lo muestra la figura 3a. El integrador es un elemento acumulador y se modela con (1)

$$\frac{X_2(z)}{X_1(z)} = \frac{1}{z-1} \quad (1)$$

Tabla 1. Resumen de características del fotodiodo pozo-n/substrato-p (n/p+)

| Descripción                                            | Magnitud            |

|--------------------------------------------------------|---------------------|

| Área fotosensible                                      | $576 \mu\text{m}^2$ |

| Factor de llenado                                      | 22.68 %             |

| Longitud de onda central                               | 700 nm              |

| Fotocurrente generada @ $P_{in}$ de $70\text{W/cm}^2$  | 1 nA                |

| Fotocurrente generada @ $P_{in}$ de $0.3\text{W/cm}^2$ | 10 pA               |

| Corriente de oscuridad                                 | 2.5 pA              |

| Máxima frecuencia de comutación                        | 100 Hz              |

Figura 2. Estructura del fotodiodo utilizado en la matriz de sensado

Figura 3. a) diagrama a bloques del  $\Sigma\Delta M$  ideal y b) modelo lineal

donde  $X_1(z)$  y  $X_2(z)$  son las señales de entrada y salida del integrador, respectivamente, como lo presenta la figura 3a.

Por otro lado, el cuantificador de 1-bit se puede linearizar al modelarlo como una fuente de ruido blanco aditivo, con varianza  $e_q^2$  y densidad espectral de potencia  $N_{eq}(f_s)$ ; esta aproximación se discute en Silva *et al.* (2009). Así, un cuantificador lineal con paso de cuantificación  $\Delta$  y ruido distribuido uniformemente en el ancho de banda, tiene una densidad espectral de potencia (PSD) dada por (2)

$$N_{eq}(f_s) = \frac{\overline{e_q^2}}{f_s} = \frac{\Delta^2}{12} \frac{1}{f_s} \quad (2)$$

donde  $f_s$  es la frecuencia de muestreo. De esta manera, el modelo se simplifica como lo presenta la figura 3b, cuya función de transferencia se obtiene por superposición. Primero haciendo  $X(z) = 0$  e incluyendo (1), se obtiene (5)

$$X_1 = -Y(z), \quad X_2 = -\frac{1}{z-1} Y(z) \quad (3)$$

$$Y(z) = E(z) + X_2(z) = E(z) - \frac{1}{z-1} Y(z) \quad (4)$$

$$Y(z) = (1 - z^{-1}) E(z) \quad (5)$$

Luego, haciendo  $E(z) = 0$  e incluyendo (1), se obtiene (6)

$$X_1 = X(z) - Y(z), \quad X_2 = Y(z) \quad (6)$$

$$Y(z) = \frac{1}{z-1} X_1(z) = \frac{1}{z-1} [X(z) - Y(z)] \quad (7)$$

$$Y(z) = z^{-1} X(z) \quad (8)$$

De esta forma, la función de transferencia del sistema de la figura 3b es (9)

$$Y(z) = z^{-1} X(z) + (1 - z^{-1}) E(z) \quad (9)$$

donde  $z^{-1}$  es la función de transferencia de la señal o STF y  $(1 - z^{-1})$  es la función de transferencia del ruido de cuantificación o NTF.

La SQNR se define como la relación entre la potencia de la señal de entrada y la potencia del ruido de cuantificación (Baker, 2010), es decir,  $SQNR = \overline{s_m^2} / \overline{s_q^2} |_{BW}$ . La potencia del ruido de cuantificación se obtiene de (10)

$$\overline{s_q^2} |_{BW} = \int_{-f_b}^{f_b} |NTF|^2 N_{eq} df = \overline{e_q^2} \cdot \frac{\pi^2}{3R} \quad (10)$$

Tabla 2. Parámetros para simulación del  $\Sigma\Delta M$  de 1er-orden y 1-bit en tiempo discreto

| Literal       | Descripción                                    | Magnitud   |

|---------------|------------------------------------------------|------------|

| $N$           | Número de bits de salida del cuantificador     | 1          |

| $V_{p(\max)}$ | Amplitud máxima de la señal de entrada (FS)    | 1.0 V      |

| $V_i(t)$      | Función de la señal de entrada                 | Sinusoidal |

| $BW = f_b$    | Ancho de banda o frecuencia máxima de la señal | 250 Hz     |

| $R$           | Razón de sobremuestreo                         | 64         |

| $f_s$         | Frecuencia de muestreo                         | 32 kHz     |

| $f_i$         | Frecuencia de la señal de entrada              | 125 Hz     |

| $N_{per}$     | Período de simulación de la señal de entrada   | 32         |

| $N_{sam}$     | Muestras a simular                             | $2^{13}$   |

| $M_O$         | Orden del modulador                            | 1          |

donde  $R$  es la razón de sobremuestreo. Para estimar  $\overline{s_m^2}$  consideramos que al modulador entra una señal sinusoidal, con frecuencia  $f_b$ , amplitud  $A_p$  y potencia  $A_p^2/2$ . Así la SQNR es (11)

$$SQNR = \frac{18R^3 A_p^2}{\pi^2 \Delta^2} \quad (11)$$

De (11), las variables posibles de optimizar son: la frecuencia de muestreo  $f_s$ , a través de  $R$  y el número de bits  $N$ , a través de  $\Delta$ . Por otro lado, con los parámetros de la tabla 2, la expresión (10) predice una SQNR de 50.77 dB, lo cual es congruente con algunos resultados encontrados en la literatura (Malcovati *et al.*, 2003).

Para verificar, se estimó la SQNR por medio de herramientas computacionales; la ventaja de estas radica en el hecho de que es posible evaluar directamente el modulador y con ello, tener una respuesta temporal. Esto permite fácilmente, agregar modelos comportamentales de fuentes de ruido presentes en un circuito modulador real.

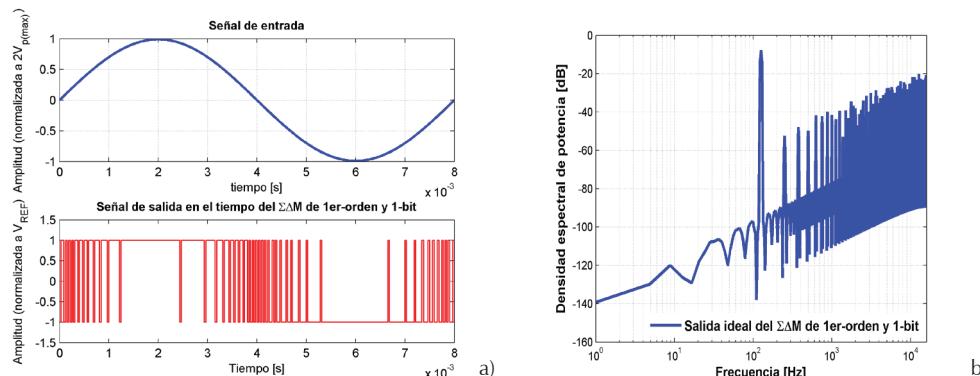

### Estimación a partir de la respuesta temporal

Para evaluar temporalmente el  $\Sigma\Delta M$  de 1er-orden y 1-bit (figura 3a) se seleccionó SIMULINK®, fundamentado en el hecho de que ha sido ampliamente utilizado para diseñar filtros paso-bajo, paso-bandas y convertidores basados en  $\Sigma\Delta M$  (Brigati, 2014). En consecuencia, el modelo de bloques se construye con las bibliotecas de SIMULINK®. Para una simulación con frecuencia de muestreo de 32 kHz y señal de entrada de 125 Hz, se obtiene un resultado temporal que se observa en la figura 4a. Este resultado muestra que una alta densidad de pulsos corresponde a valores máximos positivos y negativos de la señal de entrada; al obtener la PSD de dicha señal de salida (figura 4b), es posible estimar  $\overline{s_m^2}$  y  $\overline{s_q^2}$ .

Figura 4. a) señal de entrada y salida hacia y desde un  $\Sigma\Delta M$  de 1er orden y 1-bit, obtenido por simulación a nivel sistema, b) densidad espectral de potencia de la señal de salida del modulador

Como era de esperarse, en la figura 4b, el pico principal corresponde a la señal de entrada (125 Hz), y las componentes del ruido de cuantificación se desplazan hacia frecuencias superiores, como lo predice la NTF (comportamiento de filtro paso-alto). Para una potencia de -0.1 dB se determinó una SQNR de 52.19 dB, la discrepancia de este resultado respecto a la estimación analítica, obedece a una correlación entre la amplitud de la señal de entrada y el ruido de cuantificación. Por otro lado, la expresión (11) no impone límites a  $f_s$  y  $f_b$ , sin embargo, hay un compromiso entre los requerimientos de la aplicación y los límites tecnológicos.

Para el prototipo CIS una SQNR entre 30 y 50 dB es aceptable, requiriendo el diseño de un solo integrador. Hoy día, aplicaciones de espectrometría clínica y bioluminiscencia se implementan con  $\Sigma\Delta M$  de 1er-orden (Perelman *et al.*, 2001; Roh *et al.*, 2009; Singh *et al.*, 2011; Jung, 2013).

### Modelado de fuentes de ruido y no linealidades del circuito

El prototipo CIS se diseña con la técnica capacitor conmutado en tecnología CMOS estándar. En este tipo de diseños existen no idealidades inducidas por los componentes del modulador y también imperfecciones originadas por el sistema de caracterización. El resultado de todas las imperfecciones se adicionan al ruido de cuantificación. El ruido de cuantificación se atenúa por el lazo de retroalimentación del modulador, pero no ocurre lo mismo con las otras fuentes de ruido.

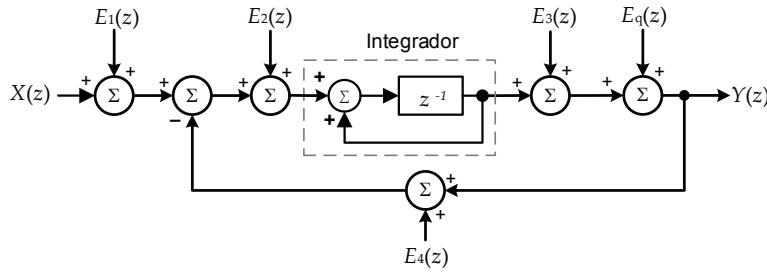

Es posible agregar fuentes de distorsión y proponer un modelo más realista como se presenta en la figura 5. La fuente  $E_1$  modela el ruido que acompaña a la señal de entrada, no linealidad del fotodiodo y ruido *clock jitter* inducido por la fase de reloj durante el muestreo.  $E_2$  incluye los efectos no ideales y el ruido referido a la entrada del integrador.  $E_3$  modela la no linealidad y el

Figura 5. Modelo del  $\Sigma\Delta M$  de 1er-orden y 1-bit, incluyendo las principales fuentes de ruido

ruido referido a la entrada del cuantificador.  $E_4$  representa el ruido referido a la entrada y por *clock jitter* de un convertidor digital-análogico (DAC), necesario para la compatibilidad de señales. Finalmente  $E_q$  es el ruido de cuantificación. La función de transferencia del nuevo sistema se presenta en (12)

$$Y(z) = z^{-1} [x(z) + E_1 + E_2 - E_4] + (1 - z^{-1})(E_q + E_3) \quad (12)$$

$E_q$  y  $E_3$  se desplazan fuera del ancho de banda de interés y  $E_1$ ,  $E_2$  y  $E_4$  se distribuyen uniformemente en toda la banda, afectando el desempeño. Así la SNR se estima con (13)

$$SNR = \frac{\overline{s_{in}^2}}{\overline{s_n^2}} \Big|_{BW} = \frac{\overline{s_{in}^2}}{\overline{s_q^2 + s_1^2 + s_2^2 + s_3^2 + s_4^2}} \Big|_{BW} \quad (13)$$

donde  $\overline{s_n^2}$  es la potencia global de ruido. En la siguiente sección se presentan los modelos útiles en la estimación de  $\overline{s_n^2}$  para la arquitectura del prototipo CIS.

Desde el punto de vista de las arquitecturas típicas de capacitor commutado en CMOS estándar, las fuentes de ruido que afectan significativamente el desempeño del modulador son las siguientes: distorsión no lineal de la señal de entrada, ruido del DAC, efecto de la velocidad de respuesta (SR) para el amplificador operacional (OpAmp), efecto  $f_u$  para el OpAmp, efecto de ganancia finita en CD para el OpAmp y ruido referido a la entrada del OpAmp.

### Distorsión no lineal debido a la señal de entrada

La fuente de luz empleada en la caracterización proviene de un LED, así es posible modular y controlar fácilmente la potencia óptica incidente sobre el CIS. La función de señal utilizada para polarizar el LED se da por (14)

$$v_i(t) = V_m \sin 2\pi f_d t \quad (14)$$

donde  $f_d$  es la frecuencia de la señal de polarización y determina el ancho de banda de la señal de entrada. Si se descarta el ruido *shot*, *flicker* y demás fenómenos que intervienen en la radiación radiativa, la potencia emitida  $p_{out}$ , como lo presenta (15), es directamente proporcional a la corriente de polarización del LED.

$$p_{out}(t) \approx P_{BK} + p_o \left[ e^{(V_B + V_m \sin 2\pi f_d t)} - 1 \right] \quad (15)$$

donde

$P_{BK}$  = potencia debido a la luz de fondo

$p_o$  = potencia de oscuridad

$V_B$  = punto de operación

$V_m$  = factor de modulación

Las variables  $P_{BK}$ ,  $p_o$ ,  $V_B$  y  $V_m$  se toman en cuenta porque introducen distorsión no lineal en la señal de salida.

Por otro lado, los fotones que inciden sobre la región activa del fotodiodo se caracterizan por su potencia óptica incidente ( $p_{in}$  en  $\text{mW/cm}^2$ ) y una respuesta espectral plana. Si se descartan los efectos de reflexión del sistema óptico y superficial del silicio, la luz incide directamente y la photocorriente generada  $i_{ph}$  es (16)

$$i_{ph}(t, \lambda) = p_{in}(t) \int_{\lambda_i}^{\lambda_f} \frac{q}{hc} \eta(\lambda) \cdot d\lambda \quad (16)$$

donde

$\eta$  = eficiencia cuántica

$q$  = carga elemental

$c$  = velocidad de la luz

Si además consideramos que cada fotón genera un par electrón-hueco y  $\eta = 1$ , la photocorriente resulta en (17)

$$i_{ph}(t) = \frac{q}{hc} \cdot p_{out}(t) \quad (17)$$

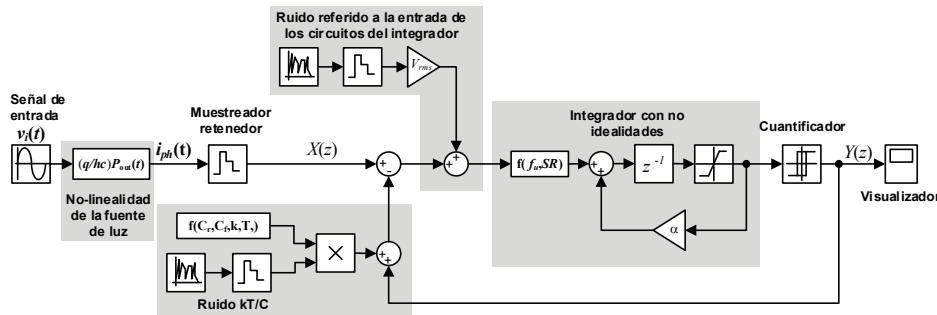

Figura 6. Modelo con fuentes de ruido y no linealidades del sistema de sensado del prototipo CIS

La distorsión por señal de entrada (11) se añadió al modelo  $\Sigma\Delta M$  de la figura 3b como un bloque modulador de la señal de entrada, este se presenta la en figura 6.

Los efectos de las no idealidades del integrador por capacitor conmutado se estudiaron ampliamente por Bourdopoulos *et al.* (2003); Boser y Wooley (2002) y Ocampo (2004). Recientemente, se presentó en Malcovati *et al.* (2003) un resumen de los modelos comportamentales para el ruido  $kT/C$ , el efecto de la velocidad de respuesta ( $SR$ ),  $f_u$  y ganancia finita en DC. Para efectos de diseño del prototipo CIS se utilizaron esos modelos.

## Resultados de simulaciones del sistema

El modelo de la figura 6 se evaluó con los parámetros de la tabla 2. Para determinar el efecto de la no linealidad de la señal de entrada se utilizó  $p_o = 92/P_{max}$  y  $V_m = 5.8$  mV, generando la PSD de la figura 7a. Los resultados muestran una SNR de 48 dB, lo que representa 4.16 dB por debajo del desempeño “ideal”. Se determinó que existe una contribución al ruido de fondo y componentes importantes de distorsión y de componente de corriente directa.

Los integradores reales tienen ganancia finita debido a una fracción de pérdida que es adicionada a cada nueva muestra a ser integrada (Boser y Wooley, 2002). Esta pérdida se modela por un factor  $\alpha$  cuyo valor se encuentra entre 0 y 1. En el modelo propuesto,  $\alpha$  es la ganancia de lazo de retroalimentación del integrador y se relaciona directamente con la ganancia del OpAmp. El efecto de  $\alpha$  se evaluó con valores cercanos a 1 (un resultado se presenta en la figura 7b). Se determinó que por debajo de 0.983, la SNR cae a 50.72 dB, apenas 1.46 dB respecto del modelo “ideal”. El efecto es una contribución importante de ruido de fondo, pero con menor distorsión armónica, respecto del efecto de la distorsión por señal de entrada.

Por otro lado, si la frecuencia unitaria  $f_u$  del OpAmp impone un tiempo menor que el tiempo de establecimiento ( $ST$ ), la ganancia del integrador se afecta. Para una adecuada operación, la máxima velocidad de res-

puesta debe ser una fracción del  $ST$ . Esta pérdida se modela con un bloque que modifica la ganancia del integrador, como se observa en la figura 6. Resultados de simulaciones, muestran que una  $f_u \geq 2f_s$  no introduce distorsión debido al  $ST$  en la señal.

El efecto de la  $SR$  se exploró, fijando  $f_u = 2f_s$ . Se concluyó que con una  $SR \geq 0.75$  V  $f_s$  se garantiza una pérdida de apenas 0.061 dB. Un aspecto de importancia en este resultado, es que el efecto del  $ST$  se traduce en una pérdida de potencia de la señal de interés y prácticamente, no hay contribución de ruido de fondo. El efecto por  $ST$  y  $f_u$  se muestra en la figura 7c.

Para el ruido referido a la entrada del OpAmp, se estimó que con  $10 \mu V/\sqrt{Hz}$  existe una pérdida de 0.16dB (figura 7d). Por otro lado, para  $C_r > 50pF$ , existirá  $100 \mu V/\sqrt{Hz}$  de ruido  $kT/C$  y pérdida de 5.8 dB (figura 7e). Debido a que el bloque DAC está en el lazo de retroalimentación, el ruido  $kT/C$  de ese bloque no presentó efecto alguno en el desempeño. Finalmente, el efecto de la tensión de saturación del integrador, trae como consecuencia un espectro como el de la figura 7f, lo que indica un fuerte incremento de componentes no lineales, una tensión de saturación mayor al paso de cuantificación ( $V_{sat} > \Delta$ ) no presenta ninguna alteración en la operación del modulador.

La tabla 3 presenta los parámetros de desempeño discutidos y se indica con  $\checkmark$  el tipo de fuente de distorsión que dicho parámetro agrega al modelo ideal.

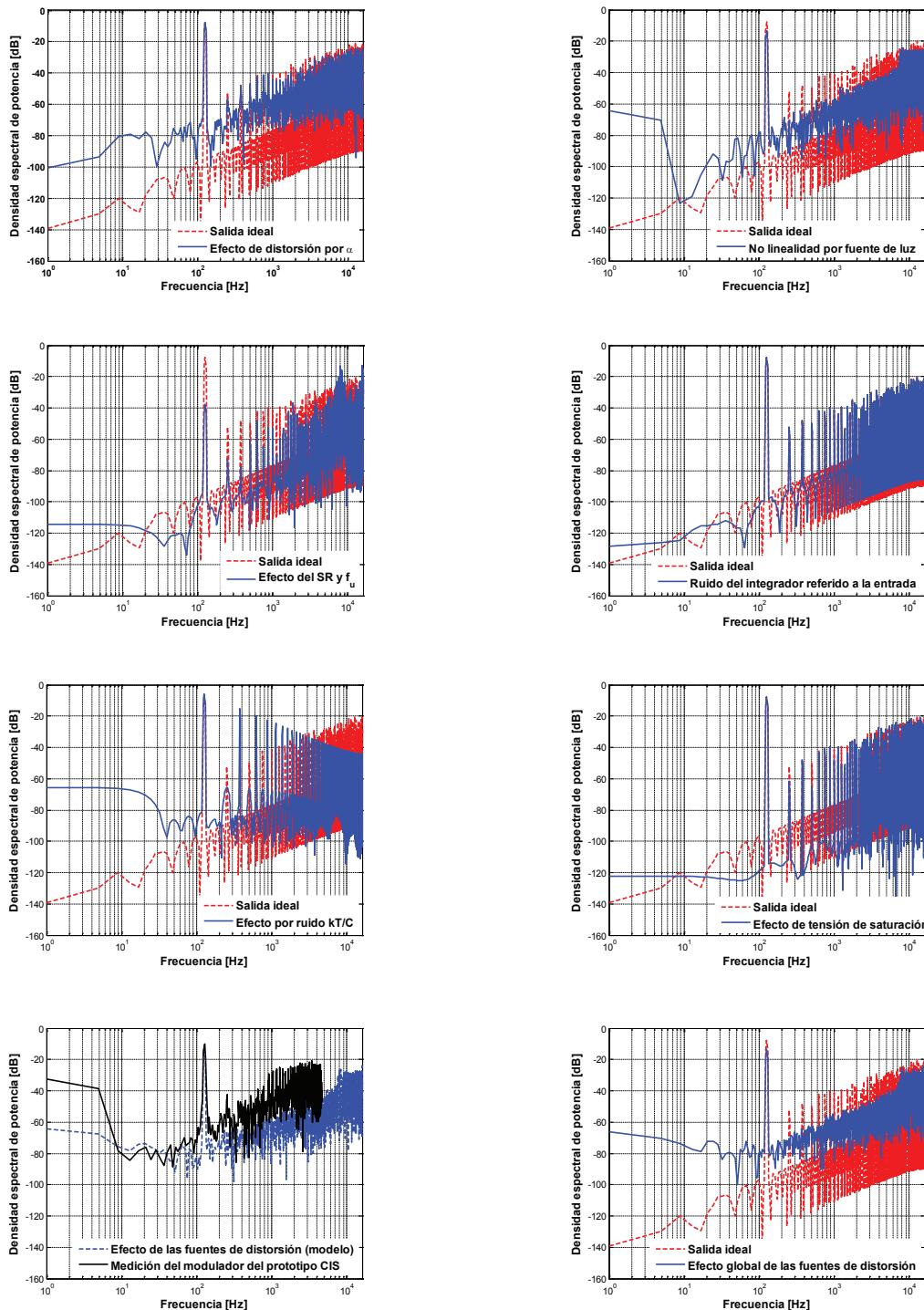

## Diseño a nivel circuito

El conjunto de especificaciones obtenidas de simulaciones a nivel sistema, se relacionaron con características eléctricas para diseñar el circuito integrador a capacitor conmutador, las dimensiones de los capacitores  $C_r$ ,  $C_i$  y características del cuantificador.

### Circuito integrador de 1er-orden

Tomando en cuenta la baja frecuencia de la señal a integrar, el alta ganancia del cuantificador, el requerimiento de polarización inversa del fotodiodo y para evitar

Figura 7. Densidad espectral de potencia de la señal de salida ante los efectos de fuentes de ruido, distorsión y no linealidades

Tabla 3. Resumen de los parámetros del modelo de la figura 8

| Parámetro de desempeño | Descripción                                               | Magnitud                                     | Ruido de fondo | Distorsión armónica | Componente de CD |

|------------------------|-----------------------------------------------------------|----------------------------------------------|----------------|---------------------|------------------|

| $p_o, V_m$             | Parámetros que originan distorsión en la señal de entrada | $p_o = 92/P_{max}$<br>$V_m = 5.8 \text{ mV}$ | ✓              | ✓                   | ✓                |

| $\alpha$               | Efecto de ganancia finita en CD                           | $\geq 0.983$                                 | ✓              |                     |                  |

| SR                     | Velocidad de respuesta                                    | $\leq 0.57 V / \Delta \cdot f_s$             |                | ✓                   |                  |

| $f_u$                  | Frecuencia unitaria                                       | $\geq 2 f_s$                                 |                | ✓                   |                  |

| $v_{ref, rms}$         | Ruido referido a la entrada del OpAmp                     | $\leq 10 \mu V / \sqrt{\text{Hz}}$           | ✓              | ✓                   |                  |

| $e_{KT/C, rms}$        | Ruido $KT/C$                                              | $Cr \geq 50 \text{ pF}$                      | ✓              | ✓                   |                  |

| $V_{sat}$              | Tensión de saturación                                     | $\geq \Delta$                                | ✓              | ✓                   |                  |

efecto de cuerpo en los MOSFETs, se seleccionó un amplificador diferencial (DifAmp) p-MOSFET, como elemento activo del integrador, como se puede ver en la figura 8 (sección integrador). El capacitor  $C_i$  y las especificaciones del DifAmp determinan el tiempo máximo de integración  $t_{int, max}$  y la precisión de conversión carga-tensión, respectivamente. La tensión de salida en el nodo  $P$  (figura 8) en la fase de integración, es (18).

$$v_o = -\frac{i_{ph}}{C_i} \int_0^{t_{int}} dt = -\frac{i_{ph} \cdot t_{int}}{C_i} \quad (18)$$

Considerando  $v_o = 1 \text{ V}$ ,  $i_{ph, max} = 10 \text{ pA}$  y  $t_{int, max} = f_b/2$ , se tiene un  $C_i$  de 200 fF. El proceso de integración se inicia después de un pulso de reinicio en  $C_i$ , generando una tensión de salida  $v_r$ , enseguida inicia el tiempo de integración y la tensión final es directamente proporcional a  $i_{ph}$  como lo indica (18). El transistor M2 en el circuito de la figura 8 se utiliza para el control del tiempo de exposición, evita también la saturación del integrador. La tabla 4 resume las características del integrador.

Figura 8. Circuito de sensado para cuatro columnas de fotodiodos

Tabla 4. Parámetros del circuito integrador

| Literal       | Descripción                  | Magnitud  |

|---------------|------------------------------|-----------|

| $C_i$         | Capacitancia de integración  | 200 fF    |

| $C_L$         | Capacitancia de carga        | ~ 180 fF  |

| $C_e$         | Capacitancia de entrada      | ~ 20 fF   |

| $R_p$         | Resistencia de apagado de M7 | ~ 100 GΩ  |

| $t_{int,max}$ | Tiempo máximo de integración | 2 ms      |

| $i_{ph,max}$  | Fotocorriente máxima         | 100 pA    |

| $A_v$         | Ganancia de lazo abierto     | 51.08 dB  |

| BW            | Ancho de banda (a -3dB)      | 30.51 kHz |

| SR            | Velocidad de respuesta       | 4.24 V/μs |

| $I_{ss}$      | Corriente de polarización    | 2 μA      |

### Circuito cuantificador de 1-bit

El circuito se presenta en la figura 8 (sección cuantificador). Se trata de un comparador de alta ganancia operado por reloj, formado por un par diferencial con p-MOSFET. Cuando ocurre  $\Phi_2$ , la tensión de salida es  $V_{thn}$ , lo que representa un 0 lógico a su salida. Cuando se presenta  $\Phi_1$  y si  $V_p > V_{REF}$ , M17 queda en corte y M16 en la región triodo, así  $V_s = 0$  V; por el contrario si  $V_p < V_{REF}$  se tiene  $V_s = V_{CC}$ . El error por desplazamiento (~20 mV) tiene poco efecto sobre la salida del modulador. El cuantificador se diseñó con ganancia lineal de voltaje de 150 y respuesta en frecuencia superior a 40 kHz.

### Diseño del convertidor digital/analógico

El circuito DAC se implementó como el propuesto en Fowler *et al.* (1994), ya que es eficiente y utiliza solo tres n-MOSFET (figura 8) (sección convertidor digital/analógico). En la fase  $\Phi_2$  se descarga  $C_{ir}$  y durante  $\Phi_1$  se habilita. Si  $v_o = 0$  V la fotocorriente continúa integrándose, disminuyendo  $V_p$ , en caso contrario  $v_o = V_{CC}$ , la fotocorriente carga a  $C_{ir}$  incrementando  $V_p$ . La relación  $C_{ir}/C_i$  determina la ganancia del integrador y es menor a 1 para garantizar estabilidad (Bourdopoulos *et al.*, 2003).

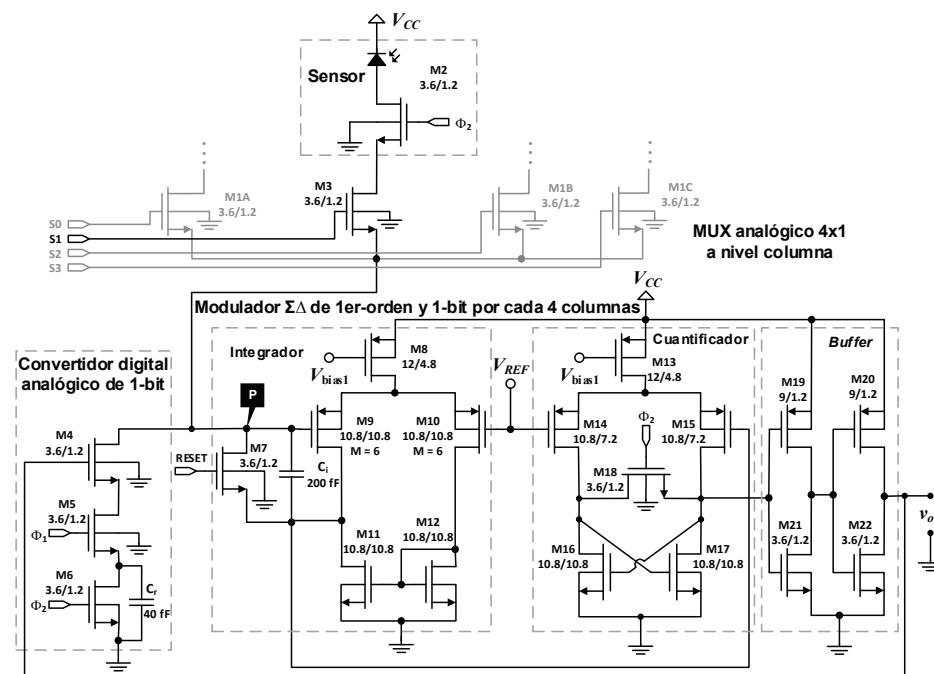

### Implementación y mediciones del prototipo sensor de imagen CMOS

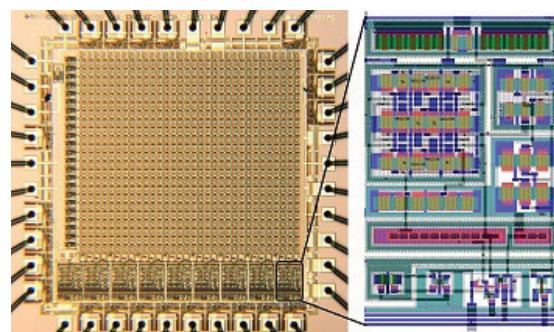

El sistema se implementó en tecnología CMOS estándar con dos capas de polisilicio y dos niveles de metal,  $\lambda_{min} = 1.2 \mu\text{m}$ , además de seguir reglas de *layout* para

sistemas de señal mixta. El metal 2 se utilizó como pantalla de luz. La figura 9 es una microfotografía del chip y el *layout*.

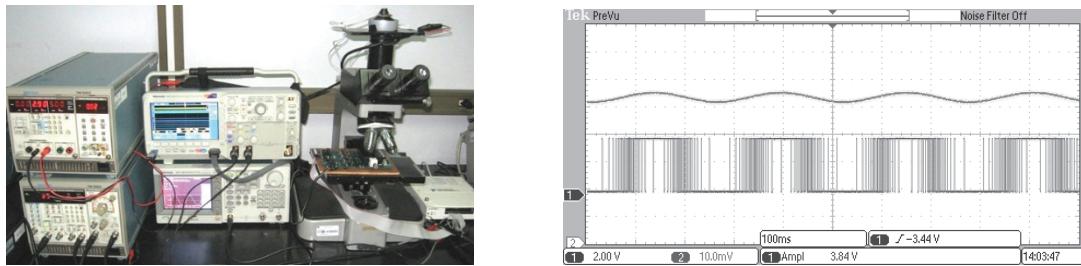

El sistema de medición se colocó sobre una base de microscopio como lo muestra la figura 10a. La fuente de luz (LED) se ubica en la parte superior. Entre la fuente de luz y la entrada del ocular se colocó una imagen impresa en acetato y se enfocó sobre la matriz de píxeles. El prototipo CIS se colocó en una PCB diseñada para este fin. Los circuitos en la PCB acondicionan la polarización, la entrada de las fases  $\Phi_1$  y  $\Phi_2$ , las entradas digitales para seleccionar la fila (reloj al registro de corrimiento) y el selector de columna (MUX analógico). Las salidas de los moduladores se capturaron con canales digitales de un osciloscopio digital, posteriormente, los datos se guardaron en dispositivos de almacenamiento extraíbles. Para realizar mediciones se seleccionó una frecuencia de muestreo de 32 kHz e intensidades de luz, desde 1 mW/cm<sup>2</sup> hasta 10 mW/cm<sup>2</sup>.

La figura 10b presenta una salida temporal, la señal superior corresponde a la tensión empleada en la polarización directa del LED, frecuencia de 3.3 Hz y amplitud de 5 mV. Con dicha amplitud se induce la mínima distorsión armónica en la luz emitida. La señal inferior es una salida de un modulador, como ya se adelantó desde la sección 3, se trata de una señal PCM cuya densidad de unos se incrementa con la máxima amplitud y con la mínima se incrementa la densidad de ceros.

Se realizaron capturas de 2 ciclos por modulador y se obtuvo la densidad espectral de potencia. Uno de esos resultados se muestra en la figura 8h, donde se adicionó la respuesta del modelo comportamental. La máxima SNR obtenida fue de 43.11 dB, que representa una pérdida de 9 dB respecto del modelo comportamental. Este resultado pone en evidencia que existe una importante contribución de componente de CD, distorsión armónica y ruido de fondo que no se consideraron en el modelo. La gran cantidad de ruido por CD lo induce la fuente de luz, ya que a nivel experimental es

Figura 9. Microfotografía del chip prototipo sensor de imagen CMOS

Figura 10. a) sistema de medición y b) señales de entrada/salida del sistema de sensado

difícil encontrar un punto de polarización que coincida con el punto de polarización del integrador. Por otro lado, son evidentes los armónicos por arriba de la frecuencia de interés, dichos componentes contribuyen a la distorsión armónica total, y naturalmente se presentan en la respuesta de un modulador de este tipo (Webb, 2009).

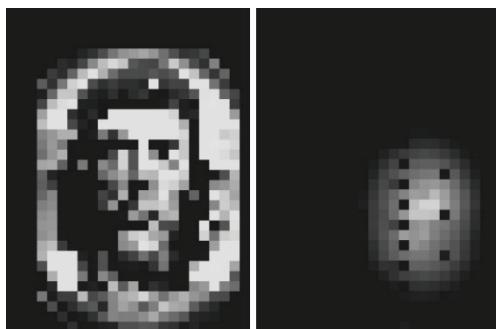

La salida digital de cada modulador se llevó a un decimador multietapa, dos etapas con filtros CIC (factor de decimación: 2) cada uno y dos etapas con filtros de rizo simétrico (factor de decimación: 4). Este proceso permitió recuperar la señal muestreada a 512 Hz ( $f_{Ny}$ ), con 8 bits. Al pasar cada salida de cada pixel por el filtro se puede correlacionar el nivel de salida digital con una escala de gris. Debido a que los niveles de salida de cada filtro garantizan 8 bits, es posible obtener hasta  $2^8$  niveles de gris. La figura 11 muestra dos ejemplos capturados con el prototipo CIS. Estos resultados muestran que las dimensiones de los pixeles y la técnica de *layout* se eligieron adecuadamente.

Figura 11. Imágenes fotografiadas con el prototipo sensor de imagen CMOS, en a) fotografía del Che-Guevara y en b) Una captura de prueba de una fuente puntual de luz

## Conclusiones

Este artículo presentó el diseño de un prototipo sensor de imagen CMOS de medianas prestaciones para fotografía digital. Los circuitos se diseñaron con base en un modelo comportamental temporal en tiempo discreto que incluye las principales fuentes de ruido originadas en la fuente de luz y los circuitos del sistema de sensado. Este último se implementó utilizando la técnica de sobremuestreo a través de un  $\Sigma\Delta M$  de 1er-orden y 1-bit, el cual desplaza el ruido de cuantificación fuera de la banda de interés. La señal de entrada es la photocorriente proveniente de un pixel formado por un fotodiodo pozo-n/substrato-p. La arquitectura del  $\Sigma\Delta M$  incluye un integrador a capacitor conmutado de 1er-orden, cuantificador, y sistema de conversión A/D. Cada bloque del modulador es una fuente particular de ruido que afecta el desempeño global, en términos de SNR. Para alcanzar una SNR específica, se utilizaron modelos de nivel sistema y simulaciones en SIMULINK®. Los resultados de análisis de la PSD mostraron que las no-linealidades de la señal de entrada son la principal fuente de distorsión a bajas frecuencias y que las no idealidades del integrador, el ruido  $kT/C$  y la saturación del cuantificador son fuentes de ruido blanco. El modelo también se empleó para la optimización de bloques de nivel circuito. Los resultados de imágenes capturadas con el CIS mostraron que el método de diseño por modelado comportamental y simulación de nivel sistema es una herramienta con alto grado de fiabilidad.

## Agradecimientos

Agradecemos al Consejo Nacional de Ciencia y Tecnología por el apoyo a esta investigación, a través del proyecto Núm. 082579.

## Nomenclatura

|        |                                                            |                  |                                       |

|--------|------------------------------------------------------------|------------------|---------------------------------------|

| ADC    | Convertidor analógico digital                              | PPS              | Sensor de pixel pasivo                |

| CIS    | Sensor de imagen CMOS                                      | PSD              | Densidad espectral de potencia        |

| CMOS   | Metal óxido semiconductor complementario                   | SCR              | Región de carga espacial              |

| DAC    | Convertidor digital analógico                              | SNR              | Razón señal a ruido                   |

| DifAmp | Amplificador diferencial                                   | SQNR             | Razón señal a ruido de cuantificación |

| LED    | Diodo emisor de luz                                        | SR               | Velocidad de respuesta                |

| MOSFET | Transistor de efecto de campo de metal óxido semiconductor | ST               | Tiempo de establecimiento             |

| OpAmp  | Amplificador operacional                                   | $\Sigma\Delta M$ | Modulador sigma-delta                 |

## Referencias

- Baker R.J. *CMOS, circuit design, layout and simulation*, IEEE Series on Microelectronic Systems, Piscataway, Nueva Jersey, Wiley-IEEE Press, 2010, pp. 230-241.

- Boser B.E., Wooley B.A. The design of sigma-delta modulation analog-to-digital converters. *IEEE Journal of Solid-State Circuits*, volumen 23 (número 6), agosto de 2002: 1298-1308.

- Bourdopoulos G.I., Pnevmatikakis A., Anastassopoulos V., Deliyannis T.L. *Delta-sigma modulators: modeling, design and applications*, Danvers, MA, World Scientific Publishing Company, 2003, pp. 139-165.

- Brigati S. Set of simulink models for the simulation of sigma-delta modulators [en línea] [fecha de consulta: 1 de abril 2014]. Disponible en: <http://www.mathworks.com/matlabcentral/leexchange/2460-sd-toolbox>.

- De La Rosa J.M. Sigma-delta modulators: tutorial overview, design guide, and state-of-the-art survey. *IEEE Transactions on Circuits and Systems—I: Regular Papers*, volumen 58 (número 1), enero de 2011: 1-21.

- El Gamal A. y Eltoukhy H. CMOS Image Sensors. *IEEE Circuits and Devices Magazine*, volumen 3, mayo-junio de 2005: 6-20.

- Fowler B., El Gamal A., Yang D.X.D. A CMOS area image sensor with pixel-level A/D conversión, en: IEEE International Solid-State Circuits Conference (41, 1994, San Francisco). Digest of Technical Papers, EU, febrero, 1994, pp. 226-227.

- Hwang Y. y Song M. Design of a CMOS image sensor based on a 10-bit two-step single-slope. *ADC*, volumen 14 (número 2), abril de 2014: 246-251.

- Jung Y., Duan Q., Roh J. A single electrode capacitive sensor using incremental delta-sigma architecture. *Analog Integrated Circuits and Signal Processing*, volumen 76 (número 2), junio de 2013: 261-265.

- Malcovati P., Brigati S., Francesconi F., Maloberti F., Cusinato P., Baschirotto A. Behavioral modeling of switched-capacitor sigma-delta modulators. *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*, volumen 50 (número 3), julio de 2003: 352-364.

- Murari K., Etienne-Cummings R., Thakor N., Cauwenberghs G. Which photodiode to use: a comparison of CMOS-compatible structures. *IEEE Sensors Journal*, volumen 9 (número 7), julio de 2009: 752-760.

- Ocampo-Hidalgo J.J. *System and circuit approaches for the design of multi-mode sigma-delta modulators with application for multi-standard wireless receivers* (doctorado en ciencias), Darmstadt, Alemania, Technischen Universität Darmstadt zur Erlangung der Würde eines, diciembre de 2004, 153 p.

- Perelman Y., Ginosar R. A low-light-level sensor for medical diagnostic applications. *IEEE Journal of Solid-State Circuits*, volumen 36 (número 10), 2001: 1553-1558.

- Proakis J.G. y Manolakis D.G. *Digital Signal Processing*, 4ta ed., EU, Prentice Hall, 2007, pp. 29-31.

- Roh H., Lee H., Choi Y., Roh J. A 0.8-v 816-nw delta-sigma modulator for low-power biomedical applications. *Analog Integrated Circuits and Signal Processing*, volumen 63 (número 1), septiembre de 2009: 101-106.

- Silva P.M., Correia V., Lanceros-Mendez S., Rocha J.G. Sigma-Delta A/D converter for CMOS image sensors, en: International Conference on Microelectronics (2009, Marrakech, Marruecos). Proc. On ICM, Marruecos, diciembre, 2009, pp. 94-97.

- Singh R.R., Bingling L., Ellington A., Hassibi A. A CMOS  $\Sigma\Delta$  photodetector array for bioluminescence-based DNA sequencing, en: Symposium on VLSI Circuits (2011, Honolulu, Hawaii), Procc. on VLSIC, IEEE, junio, 2011, pp. 96-97.

- Webb M. y Tang H. A low-power and low-complexity continuous-time GmC based Delta-Sigma modulator for WCDMA/UMTS. *International Journal of Electronics*, volumen 96 (número 6), 2009: 585-602.

**Este artículo se cita:**

**Citación estilo Chicago**

Garduza-González, Sergio, Felipe Gómez-Castañeda, José Antonio Moreno-Cadenas, Víctor Hugo Ponce-Ponce. Prototipo sensor de imagen CMOS con arquitectura de modulación a nivel columna. *Ingeniería Investigación y Tecnología*, XVII, 02 (2016): 237-249.

**Citación estilo ISO 690**

Garduza-González S., Gómez-Castañeda F., Moreno-Cadenas J.A., Ponce-Ponce V.H. Prototipo sensor de imagen CMOS con arquitectura de modulación a nivel columna. *Ingeniería Investigación y Tecnología*, volumen XVII (número 2), abril-junio 2016: 237-249.

**Semblanzas de los autores**

*Sergio Garduza-González.* Obtuvo el grado de maestro en ciencias en Cinvestav-IPN, Departamento de Ingeniería Eléctrica. Actualmente trabaja como profesor titular en la Academia de Electrónica en UPIITA-IPN. Entre sus temas de investigación se encuentran: convertidores analógico/digital por sobre-muestreo, diseño analógico en tecnología CMOS estándar, sensores de imagen CMOS, incluyendo desarrollo de métodos E-Learning para la educación superior.

*Felipe Gómez-Castañeda.* Obtuvo el grado de doctor en ciencias en Cinvestav-IPN, Departamento de Ingeniería Eléctrica. Actualmente es profesor titular del Departamento de Ingeniería Eléctrica, Cinvestav-IPN. Sus áreas de investigación son: diseño analógico de baja frecuencia, desarrollo de sistemas neuro-difusos en tecnología FPGA, sistemas adaptativos y uso de métodos de optimización basados en meta-heurística.

*Víctor Hugo Ponce-Ponce.* Obtuvo el grado de doctor en ciencias en Cinvestav-IPN, Departamento de Ingeniería Eléctrica. Actualmente está adscrito como investigador en el Laboratorio de micro-tecnología y sistemas embebidos del CIC-IPN. Sus áreas de interés son: diseño analógico de sistemas mixtos y sensores de imágenes CMOS.

*José Antonio Moreno-Cadenas.* Obtuvo el grado de doctor-ingeniero, Grenoble, Francia. Actualmente es profesor titular del Departamento de Ingeniería Eléctrica en Cinvestav-IPN. Sus áreas de investigación son: diseño analógico y mixto de sistemas en tecnología CMOS, desarrollo de sistemas neuro-difusos en tecnología FPGA, sistemas expertos basados en lógica difusa y uso de métodos de optimización para sistemas complejos.