Acta Universitaria

ISSN: 0188-6266

actauniversitaria@ugto.mx

Universidad de Guanajuato

México

Sandoval Ibarra, F.; Melchor Hernández, Natanael; Ortega Cisneros, Susana

Análisis, modelado y simulación del ruido flicker en transistores MOS

Acta Universitaria, vol. 23, núm. 5, septiembre-octubre, 2013, pp. 20-26

Universidad de Guanajuato

Guanajuato, México

Disponible en: <http://www.redalyc.org/articulo.oa?id=41629559003>

- ▶ Cómo citar el artículo

- ▶ Número completo

- ▶ Más información del artículo

- ▶ Página de la revista en [redalyc.org](http://redalyc.org)

redalyc.org

Sistema de Información Científica

Red de Revistas Científicas de América Latina, el Caribe, España y Portugal

Proyecto académico sin fines de lucro, desarrollado bajo la iniciativa de acceso abierto

## Análisis, modelado y simulación del ruido *flicker* en transistores MOS

Analysis, modeling and simulation of *flicker* noise in MOS transistors

F. Sandoval Ibarra\*, Natanael Melchor Hernández\*, Susana Ortega Cisneros\*

### RESUMEN

Para entender las causas del ruido  $1/f$  en transistores MOS se presentan las teorías que describen su origen físico, a saber, la teoría de McWhorter y la teoría de Hooge. De esa comprensión se revisan los modelos analíticos del ruido  $1/f$  reportados en la literatura, los cuales intentan correlacionar los resultados experimentales, pues esos modelos están basados en la aproximación de gran canal. Se presenta, además, una descripción de los modelos de simulación *Spice*, y se concluye que esos modelos también están basados en la teoría de dispositivos de gran canal. Por lo tanto, si la longitud del transistor debe incrementarse para minimizar el ruido  $1/f$ , es de interés conocer qué otros parámetros están bajo el control del diseñador, y qué técnica de diseño permite minimizar la magnitud de la potencia espectral de ruido. Se ofrecen resultados de simulación que muestran el desempeño del ruido ante variaciones de la longitud de canal,  $L$ , y del exponente de la frecuencia,  $\beta$ .

### ABSTRACT

In order to understand the causes of  $1/f$  noise in MOS transistors physical theories describing its physical origin, such as the McWhorter theory and the Hooge theory, are reviewed in this paper. Analytical  $1/f$  noise models correlating experimental results based on a long-channel approach have been reviewed as well. *Spice* simulation models are also described, concluding that these models are also based on the long-channel devices theory. Therefore, it is significant to find out what other parameters are under the control of the designer, and which technique can contribute to reducing the level of spectral power of the noise. Simulation results showing the noise performance when the channel length is changed,  $L$ , and the frequency power is changed,  $\beta$ .

### INTRODUCCIÓN

La tecnología *Metal-Oxide-Semiconductor* (MOS) es la dominante en la actualidad, su empleo en la industria de la microelectrónica abarca un amplio rango de aplicaciones, incluyendo analógicas, digitales y de RF. El transistor MOS, como todo dispositivo electrónico, no está exento de generar ruido electrónico. El ruido, en general, se ha descrito como una perturbación aleatoria que interfiere con las señales de interés en un circuito electrónico, y puede tener un origen intrínseco y/o extrínseco. Entonces, para diferenciar esas contribuciones conviene decir que el ruido intrínseco se ha definido como una fluctuación que depende de las propiedades fundamentales de los dispositivos electrónicos; el ruido térmico y ruido  $1/f$  son dos de las dos fuentes de ruido en transistores MOS con mayor impacto en aplicaciones analógicas (Motchenbacher & Connelly, 1993). El ruido extrínseco, por otro lado, al ser debido a efectos ajenos a los circuitos y dispositivos electrónicos, puede ser eliminado con adecuadas técnicas de blindaje; en contraste con el ruido intrínseco que solamente puede ser minimizado con un adecuado diseño a nivel circuito (Johns & Martin, 1996).

Recibido: 22 de mayo de 2013

Aceptado: 4 de octubre de 2013

**Palabras clave:**

Ruido intrínseco; baja frecuencia; transistor MOS; *Spice*.

**Keywords:**

Intrinsic noise; low frequency; MOS transistor; *Spice*.

\* Centro de Investigación y de Estudios Avanzados (CINVESTAV) del Instituto Politécnico Nacional, Unidad Guadalajara. Av. del Bosque 1145, Colonia El Bajío, Zapopan, Jalisco, C.P. 45019, Tel.: (33) 3777-3600, ext. 1057; fax: (33) 3777-3609. Correos electrónicos: sandoval@gdl.cinvestav.mx; nmelchor@gdl.cinvestav.mx; sortega@gdl.cinvestav.mx

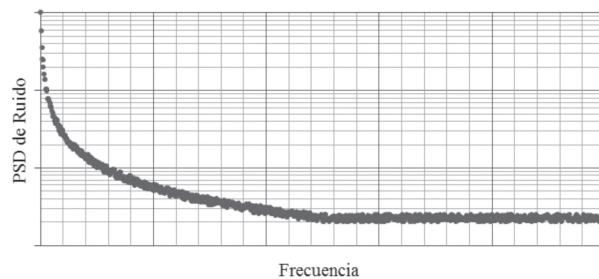

La figura 1 ilustra la característica que presenta la potencia de la Densidad Espectral (PSD por sus siglas en inglés: *Power Spectral Density*) del ruido intrínseco en transistores MOS. Obsérvese que a bajas frecuencias el ruido tiene una dependencia  $1/f$ , con lo cual es evidente que conforme la frecuencia aumenta, el ruido disminuirá hasta una frecuencia (denominada *frecuencia de esquina*), donde la PSD tendrá un espectro plano (denominado *ruido blanco*); cuando la PSD presenta un valor constante se dice que la mayor contribución es debida al ruido térmico (Celik-Butler & Vasina, 1999). Lo anterior refleja que el ruido  $1/f$  en transistores MOS es la fuente de ruido más importante a bajas frecuencias, razón por la cual en aplicaciones de baja frecuencia esta no idealidad debe ser minimizada con adecuadas técnicas de diseño. Sin embargo, para determinar qué técnicas aplicar es importante entender a qué fenómeno se enfrenta el diseñador de circuitos analógicos. En la literatura suele encontrarse que el ruido  $1/f$  también se denomina *ruido Flicker*—porque la corriente eléctrica en el medio presenta fluctuaciones que pudiesen compararse con *parpadeos*—, ruido de baja frecuencia —porque es dominante a bajas frecuencias— y ruido rosa —en analogía al color que presenta el rango inferior del espectro visible— (Baker, 2010); en esta contribución se usará el término  $1/f$ .

Figura 1. PSD del ruido intrínseco en transistores MOS.

Fuente: Elaboración propia.

La organización de esta contribución es de la siguiente manera. Primeramente, se presentan de modo breve los fundamentos de las dos teorías más aceptadas para describir el origen físico del ruido  $1/f$  en transistores MOS, de ello se hace una revisión crítica de los modelos analíticos que de aquéllas se deducen, los cuales son por lo general analizados en el contexto del modelado eléctrico equivalente de un transistor MOS de gran canal. Luego se describe cómo obtener —analíticamente— la PSD del ruido. Los modelos empíricos del ruido —reportados en la literatura—, y cómo modelar su efecto en circuitos complementarios (CMOS), se analizan posteriormente. Las consideraciones de diseño para minimizar la PSD del ruido en

transistores MOS son presentadas en la misma sección. Luego, para determinar cómo se realiza el análisis del ruido  $1/f$  en programas de simulación de propósito general —como Spice— se hace una revisión de los modelos de simulación reportados en la literatura. En esta misma sección se ofrece una comparación de resultados, modelos analíticos *vs* modelos Spice, con el propósito de mostrar si entre uno y otro modelado existe correlación. Finalmente se exponen las conclusiones de esta contribución y se ofrece una breve descripción del trabajo futuro.

#### Teorías del origen físico del ruido $1/f$

El origen físico del ruido  $1/f$  en transistores MOS es, estrictamente hablando, incierto. Si bien hay intentos por describirle, también es verdad que aquéllos aún causan polémica en la comunidad debido al grado de incertidumbre que se tiene —en cuanto a su origen— al ser muchas las teorías que intentan explicarlo. Las teorías de mayor aceptación son dos: la fluctuación en el número de portadores y la fluctuación en la movilidad de portadores en el canal.

##### ▫ Teoría de McWhorter, $\Delta N$

La teoría de la fluctuación en el número de portadores fue propuesta por McWhorter (1957). Según esa teoría, en el canal de conducción ocurre un intercambio de portadores de carga con las trampas existentes en la interface con el óxido ( $\text{SiO}_2$ ), y ocurre mediante distintos tipos de transición que incluyen procesos activados térmicamente o por tuneldeo; según esta teoría, el intercambio que se presenta depende de la naturaleza de la trampa y de las condiciones de polarización del transistor. En esta propuesta se asume, además, que se presenta una dependencia exponencial en la tasa de captura/liberación que se relaciona con la profundidad de la trampa en el óxido. Aún más, se asume una distribución uniforme en el espacio, y en la energía también, lo que significa que se presenta una distribución de trampas ( $N_{ot}$ ) que se distribuyen uniformemente en el canal de conducción. En consecuencia, la PSD asociada al número de trampas —ocupadas por unidad de área,  $S_{N_{ot}}(f)$ — suele representarse por:

$$S_{N_{ot}}(f) = N_{ot} WL \frac{1}{f}, \quad (1)$$

donde  $W$  y  $L$  son, respectivamente, el ancho y largo del canal, y  $f$  la frecuencia de interés. Es importante señalar que la teoría de McWhorter está basada en transistores MOS de gran canal (Celik-Butler & Vasina, 1999). Obsérvese, según esta propuesta, que para minimizar la generación de ruido *flicker* los úni-

cos parámetros bajo el control del diseñador son la dimensión física del transistor, lo cual implica reducir el área efectiva del canal de conducción; esta conclusión, en la práctica, no se verifica porque para minimizar la generación de ruido la dimensión física del transistor suelen ser incrementada (Nemirovsky, Brouk & Jakobson, 2001). Además, cuando el transistor es parte de un circuito o sistema de procesamiento de señales —fundamentalmente analógicas— aumentar el área del transistor implica incrementar el valor de las capacitancias parásitas, lo que se traduce en una reducción en el ancho de banda. Puede concluirse que la correlación con la experiencia no se alcanza con (1), sino con diversos modelos empíricos que han sido desarrollados con el transcurrir del tiempo.

▫ Teoría de Hooge,  $\Delta\mu$

En esta teoría se propone que la movilidad de portadores —en el canal de conducción— experimenta fluctuaciones que son consecuencia del atrapamiento de portadores de carga por las trampas situadas en el óxido, las que actúan como sitios de Coulomb. La relación empírica que se usa para cuantificar la PSD del ruido como un equivalente en corriente,  $S_p$ , en una muestra homogénea, está dada por:

$$S_p = \frac{\alpha I^2}{N} \cdot \frac{1}{f}, \quad (2)$$

donde  $I$  y  $N$  son la corriente promedio y el número total de portadores en la muestra, respectivamente, y  $\alpha$  es el parámetro empírico de Hooge con un valor aproximado de  $2.0 \times 10^{-3}$ . En la práctica, el modelo analítico asociado a la teoría de la fluctuación en la movilidad de portadores presenta mayor correlación con la observación experimental, y en particular en dispositivos de canal corto (Masson, Ghibaudo, Autran, Morfouli & Brini, 1998), pues se verifica que al reducir la longitud de canal aumenta la magnitud de la corriente  $I$ , y consecuentemente la PSD. En otras palabras, porque es deseable minimizar la PSD, el diseñador de circuitos suele incrementar solamente la longitud de canal. Sin embargo, para cuantificar la reducción del ruido  $1/f$  en transistores MOS —usados en aplicaciones analógicas— y también a nivel circuito, el diseño se realiza en términos de las propiedades de un transistor MOS de gran canal (Nemirovsky, Corcos, Brouk, Nemirovsky & Chaudhry, 2011). En la práctica, si bien es cierto que es un error de método usar una aproximación de gran canal cuando los diseños se realizan en tecnología de canal corto, también es verdad que usar el simulador como herramienta única de diseño no sólo aleja al diseñador de la comprensión del fenómeno físico, sino que

procederá de la misma manera cada vez que tenga necesidad de realizar un nuevo diseño. Este escenario da lugar a las siguientes consideraciones:

- ¿Cuál es la conveniencia de usar el simulador? Si el propósito es participar del *estado del arte*, se pueden usar los recursos de optimización —del simulador—, seleccionar el modelo del ruido, incorporar los parámetros tecnológicos que correspondan y *generar* soluciones de simulación susceptibles de ser reportadas a la comunidad. En otras palabras, el diseño así obtenido se asume *óptimo* por cuanto no se duda de las capacidades del simulador; cuando el uso de un simulador particular es un estándar tanto de la industria como de la academia, suele asignársele la categoría de *sinónimo de verdad*. No se pone en duda sus capacidades, incluso sin importar qué algoritmos tiene incorporados. Por el contrario, si el fin último no es participar del *estado del arte* sino sólo cuantificar el ruido generado en un transistor, o en un diseño particular, lo primero que debe hacerse es seleccionar el modelo del ruido, incorporar los parámetros tecnológicos que correspondan y obtener un resultado de simulación que permita compararle con ese resultado numérico, obtenido de un modelo empírico. Esa comparación, en otras palabras, es un intento por evaluar la correlación entre ambos resultados, y ésta suele ser menor al 1%. La razón es simple, independientemente del modelo de simulación del transistor, los modelos de ruido del simulador son los modelos empíricos reportados en la literatura.

Un alto porcentaje de los modelos analíticos reportados para cuantificar el ruido  $1/f$  están basados en la aproximación de gran canal. La razón no sólo es porque el diseñador tiene bajo su control los únicos parámetros controlables del transistor (largo y ancho del canal de conducción), sino porque para correlacionar la evidencia experimental el diseñador incrementa —necesariamente— la longitud del canal. En la práctica, si bien el ruido  $1/f$  está presente en otros dispositivos electrónicos, en todos ellos esta clase de ruido está asociado a la existencia de una corriente en directa (DC) que fluye por un medio discontinuo, y esta característica puede deberse tanto a las imperfecciones en la estructura cristalina del semiconductor (incluyendo impurezas indeseadas), como a los diversos mecanismos de dispersión existentes entre los portadores de carga y las trampas, entendidas éstas como niveles de energía superficial del semiconductor (Vasilescu, 2005).

### Modelado del ruido $1/f$ en transistores MOS

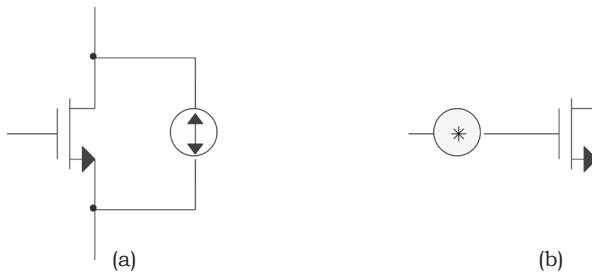

Para comprender el efecto del ruido a nivel modelo eléctrico equivalente, la figura 2 muestra cómo representar el ruido en transistores MOS (Baker, 2010). El ruido generado por un transistor puede representarse como una fuente equivalente en corriente conectada entre la terminal de drenaje y fuente del transistor,  $S_{ld}$ . Alternativamente una fuente equivalente en voltaje puede conectarse en serie con la terminal de compuerta del dispositivo,  $S_{Vg}$ . Esta última es de utilidad porque permite comparar la magnitud del ruido generado con la magnitud de las señales de interés.

**Figura 2.** Modelo eléctrico equivalente al ruido generado por un transistor MOS, como una fuente de corriente (a), y como una fuente equivalente en voltaje referida a la entrada del transistor.

Fuente: Elaboración propia.

Con ayuda de la ley de Ohm es inmediato obtener la PSD de un dispositivo MOS, es decir, si  $dI_d = g_m dV_g$  entonces  $S_{ld} = g_m S_{Vg}$ . Nótese que con los postulados de la teoría de semiconductores se determina la PSD asociada a las fluctuaciones en el número de trampas ocupadas, con lo cual sólo resta determinar un modelo —basado en la teoría de operación del transistor MOS de canal largo— que defina la relación entre el número de trampas en el óxido, el número de portadores en el canal, las dimensiones geométricas del transistor y los parámetros eléctricos en el punto de operación ( $I_d$ ,  $V_d$ ,  $V_g$ ). Entonces, se ha reportado en la literatura que las densidades de carga eléctrica en el canal de inversión y de las trampas en el óxido están dadas, respectivamente, por:

$$Q_{inv} \left[ \frac{C}{cm^2} \right] = \frac{qN_{inv}}{WL}, \quad (3)$$

y

$$Q_{ot} \left[ \frac{C}{cm^2} \right] = \frac{qN_{ot}}{WL}, \quad (4)$$

donde  $N_{inv}$  es el número total de portadores en el canal y  $N_{ot}$  representa el número total de trampas ocupadas (Jakobson, Bloom & Nemirovsky, 1988). Luego, de acuerdo con la teoría del transistor MOS:

$$\delta Q_{inv} = - \left[ \frac{C_{inv}}{C_{ox} + C_d + C_{inv}} \right] \delta Q_{ot}, \quad (5)$$

donde  $C_d$  es la capacitancia de agotamiento,  $C_{ox}$  es la capacitancia del óxido y  $C_{inv}$  es la capacitancia asociada a la región de inversión; todas expresadas en capacitancia por unidad de área. Entonces, para un análisis en pequeña señal se tiene que:

$$S_{Q_{inv}}(f) = \left[ \frac{C_{inv}}{C_{ox} + C_d + C_{inv}} \right]^2 S_{Q_{ot}}(f), \quad (6)$$

donde,

$$S_{Q_{ot}}(f) = \left[ \frac{q}{WL} \right]^2 S_{N_{ot}}(f), \quad (7)$$

y  $S_{N_{ot}}(f)$  está dada por (1). Sustituyendo ambas expresiones en (6) se tiene que:

$$S_{Q_{inv}}(f) = \left[ \frac{C_{inv}}{C_{ox} + C_d + C_{inv}} \right]^2 \frac{q^2 N_{ot}}{WL} \frac{1}{f}. \quad (8)$$

Obsérvese que este resultado muestra qué relación guarda el número de portadores en el canal —a través del número de trampas ocupadas— y la dimensión física del transistor, con lo cual lo que sigue es incorporar la dependencia del punto de polarización. Entonces, para simplificar (8) debe tenerse presente que en aplicaciones analógicas el transistor opera en régimen de fuerte inversión, y según la teoría del transistor MOS  $C_{inv} \gg C_{ox} + C_d$ , con lo cual la PSD de la carga en la región de inversión se simplifica:

$$S_{Q_{inv}}(f) = \frac{q^2 N_{ot}}{WL} \frac{1}{f}. \quad (9)$$

En aplicaciones analógicas, el transistor MOS suele polarizarse en su región de saturación, donde el voltaje de drenaje  $V_d$  que define el límite entre la región lineal y de saturación se denomina voltaje de saturación,  $V_{d,sat}$ . En la práctica, para asegurar que el transistor MOS opera en saturación debe satisfacerse que  $V_d \gg V_{d,sat} \approx V_g - V_{th}$  (Baker, 2010). Esta condición de polarización presenta una no idealidad, y es el denominado fenómeno de *pinch-off*, lo que significa que el canal de conducción no es uniforme y que la carga eléctrica en él es función de la distancia,  $y$ , a lo largo del canal:

$$Q_{inv}(y) = C_{ox} \left[ V_g - V_{th} - V(y) \right], \quad (10)$$

donde  $V(y)$  varía de 0 en  $y = 0$  a  $V_{d,sat} \approx V_g - V_{th}$  en  $y = L$  (que es donde ocurre el fenómeno de *pinch-off*).

La ecuación (10) es importante porque es el modelo a través del cual suele relacionarse la densidad de carga tanto con el voltaje aplicado en la terminal de compuerta,  $V_g$ , como con el voltaje de encendido,  $V_{th}$ . Entonces, la carga promedio en la región de inversión se obtiene de (Valenza, Hoffmann, Sodini, Laigle, Martínez & Rigard, 2004):

$$Q_{inv} = \frac{1}{L} \int_0^L Q_{inv}(y) dy = \frac{C_{ox}}{L} \int_0^{V_g - V_{th}} \left[ V_g - V_{th} - V(y) \right] \frac{dV}{dV}. \quad (11)$$

Esta expresión puede resolverse al multiplicarle por  $Q_{inv}/Q_{inv}$  y considerando que  $Q_{inv}(dV/dy) = I_d/W\mu y$  y que en saturación la corriente,  $I_d$ , es constante a lo largo de todo el canal, se tiene que:

$$I_d = \frac{C_{ox}\mu W}{2L} (V_g - V_{th})^2, \quad (12)$$

donde  $\mu$  es la movilidad de portadores (a saber tipo N o tipo P). Entonces se obtiene que:

$$Q_{inv} = \frac{2}{3} C_{ox} (V_g - V_{th}), \quad (13)$$

En consecuencia,

$$S_{Q_{inv}}(f) = \frac{4}{9} C_{ox}^2 S_{V_g}(f). \quad (14)$$

Para relacionar  $S_{Q_{inv}}(f)$  con  $N_{ot}$ , la relación de capacidades en (8) debe promediarse a lo largo del canal. En  $y = 0$ , cerca de la terminal de fuente, la fuerte inversión prevalece, con lo que  $C_{inv} \gg C_{ox} + C_d$ , adquiriendo la relación de capacitores un valor equivalente a 1. Por el contrario, en el punto de *pinch-off*,  $C_{inv} = 0$  y la relación capacitiva tiende a cero. Por lo tanto,  $S_{Q_{inv}}(f)$  está relacionada a  $N_{ot}$  por un factor aproximado de  $\frac{1}{2}$  (Jakobson *et al.*, 1988):

$$S_{Q_{inv}}(f) = \frac{1}{2} \frac{q^2 N_{ot}}{WL} \frac{1}{f}. \quad (15)$$

Nótese que la diferencia entre (9) y (15) es que en la obtención de aquélla se asume que el canal de inversión es uniforme, mientras que en (15) se deduce a través de incorporar el fenómeno de *pinch-off*. Este último resultado, si bien es una aproximación simple, permitiría proponer por qué —en un transistor en saturación— se satisface que  $C_{inv} \gg C_{ox} + C_d$ . Luego, al igualar (9) con (14) se obtiene que:

$$S_{V_g}(f) = \frac{9}{8} \frac{q^2 N_{ot}}{C_{ox}^2 WL} \frac{1}{f} \approx \frac{q^2 N_{ot}}{C_{ox}^2 WL} \frac{1}{f}. \quad (16)$$

Este resultado indica, por un lado, que la PSD del voltaje  $V_g$  —que garantiza que el transistor opere en saturación— incorpora la dependencia con la densidad de trampas y, por otro lado, representa la potencia

espectral del ruido referido a la entrada, mostrada en la figura 2b; este resultado es importante porque permite incorporarle como una fuente equivalente de voltaje y analizar su efecto a nivel circuito con los postulados de la teoría de circuitos. Puede demostrarse que  $[SV_g] = V^2/Hz$ , y con ayuda de la ley de Ohm obtener la PSD del ruido equivalente en corriente,  $S_{Id}(f) = g_m^2 S_{V_g}(f)$ :

$$S_{I_d}(f) \approx \frac{2q^2 \mu N_{ot} I_d}{C_{ox} L^2} \frac{1}{f}. \quad (17)$$

Obsérvese que este resultado justificaría por qué, para minimizar el ruido generado por un transistor, se recomienda incrementar el largo del canal de conducción (Jakobson, Bloom & Nemirovsky, 1996); este resultado también muestra por qué un transistor MOS tipo P genera menor cantidad de ruido que su contraparte tipo N; recuérdese que  $\mu_p < \mu_n$  (Nemirovsky *et al.*, 2011). Para todo propósito práctico, tanto (16) como (17) deben considerarse modelos analíticos de diseño, sin olvidar que falta determinar un valor típico y/o una expresión para  $N_{ot}$ .

#### Modelos analíticos de ruido 1/f en transistores MOS

La PSD debida al ruido —equivalente en corriente—,  $S_{Id}$ , en función de  $g_m$  reportada en la literatura está dada por:

$$S_{I_d}(f) = \frac{q^2 N_{ot} g_m^2}{C_{ox}^2 WL} \cdot \frac{1}{f^\beta}, \quad (18)$$

donde  $\beta$  es una constante que satisface  $0.7 < \beta < 1.3$  (Brouk & Nemirovsky, 2004). Alternativamente se ha reportado otra forma analítica para la PSD:

$$S_{I_d}(f) = \frac{2q^2 N_{ot} \alpha I_d}{C_{ox} L^2} \cdot \frac{1}{f^\beta}, \quad (19)$$

la cual es útil pues permite diferenciar el ruido generado por uno u otro tipo de transistor MOS, a saber tipo N o tipo P.

En el diseño de circuitos en modo voltaje, el análisis resulta más significativo al representar el ruido generado como un equivalente en voltaje y referido al nodo de entrada del dispositivo. El modelo empírico reportado está dado por (Brouk & Nemirovsky, 2004):

$$S_{V_g}(f) = \frac{S_{I_d}(f)}{g_m^2} = \frac{q^2 N_{ot}}{C_{ox}^2 WL} \cdot \frac{1}{f^\beta}, \quad (20)$$

donde  $\beta$  es un parámetro que suele obtenerse de resultados experimentales (Nemirovsky *et al.*, 2011), es decir, es un parámetro de ajuste; por ajuste debe

entenderse que es una manera ruda de correlacionar la teoría con la evidencia experimental, con lo cual la pregunta natural sería ¿qué principio físico justificaría un valor  $\beta \neq 1$ ?

### Modelos Spice del ruido 1/f en transistores MOS

Luego de diseñar un circuito es fundamental su simulación, y no sólo para verificar el cumplimiento de especificaciones sino para acceder a los recursos de optimización de la herramienta de simulación. En lo que al análisis del ruido se refiere, el modelo *Spice* de mayor uso para el análisis de ruido 1/f en transistores MOS —operando en fuerte inversión— es *Spice-Flicker noise* (Lui, 2001), NLEVEL = 0:

$$S_{I_d}(f) = \frac{KF \cdot I_d^{AF}}{C_{ox} \cdot L^2} \cdot \frac{1}{f^{EF}}, \quad (21)$$

donde *KF*, *AF*, y *EF* son el coeficiente *flicker*, y los exponentes de la corriente y de la frecuencia, respectivamente; al valor del coeficiente *KF* se le asocia una dependencia con el proceso tecnológico, y *AF* tiene un valor por *default* de 1 (Cheng *et al.*, 1996). Otro modelo *Spice*, denominado NLEVEL=1, está dado por:

$$S_{I_d}(f) = \frac{KF \cdot I_d^{AF}}{C_{ox} \cdot WL} \cdot \frac{1}{f^{EF}}. \quad (22)$$

Un tercer modelo, NLEVEL=2&3, es ése que el simulador ejecuta por *default*, y está dado por:

$$S_{I_d}(f) = \frac{KF \cdot g_m^2}{C_{ox} \cdot WL} \cdot \frac{1}{f^{EF}}. \quad (23)$$

En la práctica, los modelos de ruido 1/f ejecutados por *Spice* incluyen valores por *default* (de valor 1) que reducen los modelos de la PSD a los modelos analíticos (18) y (19). Sin embargo, porque la comunidad se ha dado a la tarea de determinar parámetros de ajuste es que *Spice acepta* que el diseñador introduzca los valores que correspondan en el modelo de simulación (Baker, 2010); esta posibilidad permite obtener el mejor ajuste entre los resultados de simulación y los obtenidos experimentalmente (Bonani & Ghione, 2002; Spencer & Ghausi, 2003). Para aquellas situaciones en el que no se cuenta con información experimental, los valores por *default Spice* son *AF=EF=1*, y para *KF* el valor típico es  $10^{-28}$ ; este último debe ser introducido en el modelo de simulación CMOS (Baker, 2010). Obsérvese que, al comparar (19) con (21) y (18) con (23), se tiene que:

$$KF = 2q^2 N_{ot} \mu, \quad (24)$$

$$KF'' = \frac{q^2 N_{ot}}{C_{ox}}. \quad (25)$$

## RESULTADOS

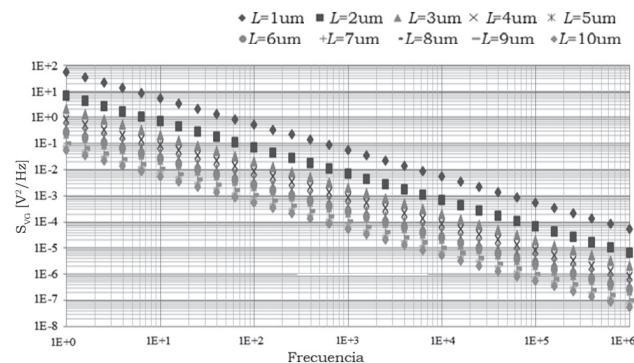

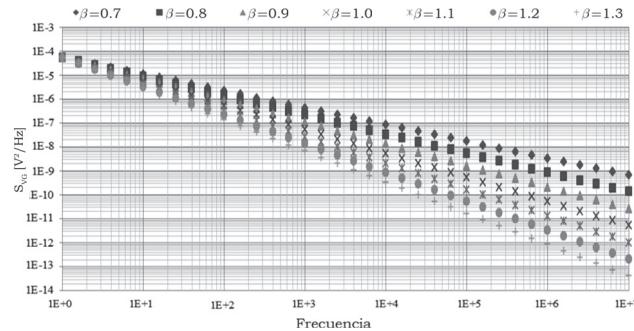

Se realizó la simulación del ruido 1/f en *TSpice* para visualizar el impacto de la longitud de canal, *L*, y el exponente de la frecuencia,  $\beta$ . Como aún no se tienen datos experimentales, se normalizaron los coeficientes *Spice* a un valor equivalente a 1.

La gráfica de la figura 3 muestra que el aumento de la longitud del canal disminuye, en efecto, el ruido 1/f en varios órdenes de magnitud. Es importante lo anterior, ya que la longitud de canal de los transistores es un parámetro bajo el control del diseñador.

La gráfica mostrada en la figura 4 muestra la importancia de  $\beta$ , el exponente de la frecuencia, parámetro que permite extender la frecuencia esquina varios órdenes de magnitud, haciendo que el ruido 1/f impacte a frecuencias mayores, como ha sido reportado en la literatura especializada (Brouk & Nemirovsky, 2004).

Figura 3. Comparación de la PSD de ruido de  $V_{GS}$  a diferentes longitudes de canal, con  $W=10\mu\text{m}$ ,  $V_{GS} = V_{DS} = 2.5\text{V}$ .

Fuente: Elaboración propia.

Figura 4. Comparación de la PSD de ruido de  $V_{GS}$  a diferentes exponentes de frecuencia,  $\beta$ , de canal, con  $W=L=10\mu\text{m}$ ,  $V_{GS} = V_{DS} = 2.5\text{V}$ .

Fuente: Elaboración propia.

## DISCUSIÓN

De las dos teorías del origen del ruido  $1/f$  expuestas, se omite la teoría de la fluctuación de la movilidad para el análisis en transistores de canal largo, ya que en la práctica tiene mayor correlación en dispositivos de canal corto, pues al reducir la longitud de canal aumenta la corriente  $I$  y, consecuentemente, la PSD.

Es bien sabido que los transistores MOS de canal largo presentan menores niveles de ruido  $1/f$  respecto a su contraparte de canal corto, notándose esta característica en la dependencia  $L^2$  de la PSD.

La presencia de niveles mayores de ruido en transistores MOS tipo N se atribuye a un menor nivel de la barrera de tuneldeo, 3.1 eV para electrones, mientras que 4.8 eV para huecos, así como la diferencia de la masa efectiva entre estos dos portadores y las movilidades de canal. Lo anterior se interpreta de la siguiente manera: es más probable que las trampas en el óxido capturen portadores mayoritarios negativos que positivos.

Los modelos de simulación *Spice* se ajustan a los modelos de canal largo propuestos, sin embargo es necesaria la caracterización experimental de transistores para la extracción de los coeficientes de ruido, para así tener resultados de simulación que correlacionen lo más posible los resultados experimentales; el problema nuevo es determinar qué fenómeno justificaría que  $\beta \neq 1$ , ya que el exponente de la frecuencia —según reportes en la literatura— puede variar en un rango de  $0.7 < \beta < 1.3$ , y tener certeza de ese valor es fundamental pues incide en el valor de la frecuencia esquina; para el rango de valores señalado, la frecuencia esquina oscila entre varios órdenes de magnitud y puede alcanzar frecuencias de varias decenas de kHz.

Finalmente, el trabajo a futuro incluye la medición experimental del ruido  $1/f$  en transistores MOS y del análisis de datos inferir los parámetros *Spice* que permitan simular y, consecuentemente, correlacionar el desempeño del ruido  $1/f$  y establecer también el valor de la frecuencia esquina. Los detalles del arreglo experimental y qué precauciones deben tomarse en cuenta son tema de otra contribución, pues las metodologías de captura de datos son diversas.

## REFERENCIAS

- Baker, R. J. (2010). *CMOS: Circuit Design, Layout, and Simulation*. New Jersey: John Wiley & Sons, Inc.

- Bonani, F. & Ghione, G. (2002). *Noise in Semiconductor Devices: Modeling and Simulation*. New York: Springer-Verlag Publishers.

- Brouk, I. & Nemirovsky, Y. (2004). *Noise Characterization of the 0.35  $\mu$ m CMOS Analog Process Implemented in Regular and SOI Wafers*. Trabajo presentado en Proceeding 11th IEEE Internacional Conference on Electronics, Circuits and Systems. Tel Aviv, Israel.

- Celik-Butler, Z. & Vasina, P. (1999). Channel length scaling of  $1/f$  noise in 0.18 mm technology MDD n-MOSFETs. *Solid-State Electronics*, 43(9), 1695-1701.

- Cheng, Y., Chan, M., Hui, K., Min-chie, J., Liu, Z., Huang J., Chen, K., Chen, J., Tu, R., Ko, P. K. & Chreming, H. (1996). *BSIM3v3 Manual*. Department of Electrical Engineering and Computer Sciences, University of California: Berkeley.

- Jakobson, C., Bloom, I. & Nemirovsky, Y. (1988). *1/f Noise in CMOS Transistors for Analog Applications from Subthreshold to Saturation*. Trabajo presentado en 19th Convention of Electrical and Electronics Engineering. Israel.

- Jakobson, C., Bloom, I. & Nemirovsky, Y. (1996). *1/f noise in CMOS Transistors for Analog Applications*, Trabajo presentado en 19th Convention of Electrical and Electronics Engineering. Israel.

- Johns, D. A. & Martin, K. (1996). *Analog Integrated Circuit Design* (1st ed). San Francisco: John Wiley & Sons, Inc.

- Lui, W. (2001). *MOSFET Models for SPICE simulation including BSIM3v3 and BSIM4*. New Jersey: IEEE Computer Society Press.

- Masson, P., Ghibaudo, G., Autran, J. L., Morfouli, P. & Brini, J. (1998). Influence of quadratic mobility degradation factor on low frequency noise in MOS transistors. *Electronics Letters*, 34(20), 1977-1979.

- McWhorter, A. L. (1957). *Semiconductor Surface Physics*. New Jersey: University of Pennsylvania Press.

- Motchenbacher, C. D. & Connelly, J. A. (1993). *Low Noise Electronic System Design*. New York: John Wiley & Sons, Inc.

- Nemirovsky, Y., Brouk, I. & Jakobson, C. G. (2001). *1/f noise in CMOS Transistors for Analog Applications*. *IEEE Transactions on Electron Devices*, 48(5), 921-927.

- Nemirovsky, Y., Corcos, D., Brouk, I., Nemirovsky, A. & Chaudhry, S. (2011). *1/f Noise in Advanced CMOS Transistors*. *IEEE Instrumentation & Measurement Magazine*, 14(1), 2-10.

- Spencer, R. & Ghausi, M. (2003). *Introduction to Electronic Circuit Design*. San José: Prentice-Hall Publishers.

- Valenza, M., Hoffmann, A., Sodini, D., Laigle, A., Martínez, F. & Rigard, D. (2004). Overview of the Impact of Downscaling Technology on  $1/f$  Noise in p-MOSFETs: Noise in Devices and Circuits, *IEE Proceedings on Circuits Devices and Systems*, 151(2), 102-110.

- Vasilescu, G. (2005). *Electronic Noise and Interfering Signals*. París: Springer Series on Signals and Communication Technology.