Journal of Applied Research and Technology

ISSN: 1665-6423

jart@aleph.cinstrum.unam.mx

Centro de Ciencias Aplicadas y Desarrollo

Tecnológico México

Sánchez-López, C.; Martínez-Romero, E.; Tlelo-Cuautle, E.

Symbolic Analysis of OTRAs-Based Circuits

Journal of Applied Research and Technology, vol. 9, núm. 1, abril, 2011, pp. 69-80

Centro de Ciencias Aplicadas y Desarrollo Tecnológico

Distrito Federal, México

Available in: http://www.redalyc.org/articulo.oa?id=47419311006

Complete issue

More information about this article

Journal's homepage in redalyc.org

## **Symbolic Analysis of OTRAs-Based Circuits**

C. Sánchez-López\*1,2, E. Martínez-Romero3, E. Tlelo-Cuautle3

<sup>1</sup>Department of Electronics, UAT, Mexico Czda Apizaquito s/n, Apizaco, Tlaxcala, 140. <sup>2</sup>IMSE-CNM, CSIC and University of Seville, Spain Avda. Americo Vespucio s/n, Isla de la Cartuja, Sevilla, 41090 \*carlsanmx@yahoo.com.mx <sup>3</sup>Department of Electronics, INAOE, Mexico Luis Enrique Erro No. 1 Tonantzintla, Puebla, 72840

## **ABSTRACT**

A new nullor-based model to describe the behavior of Operational Transresistance Amplifiers (OTRAs) is introduced. The new model is composed of four nullors and three grounded resistors. As a consequence, standard nodal analysis can be applied to compute fully-symbolic small-signal characteristics of OTRA-based analog circuits, and the nullor-based OTRAs model can be used in CAD tools. In this manner, the fully-symbolic transfer functions of several application circuits, such as filters and oscillators can easily be approximated.

Keywords: Operational Transresistance Amplifier, nullor, nodal analysis.

#### RESUMEN

En el presente trabajo se presenta un nuevo modelo basado en nullors para describir el comportamiento de amplificadores operacionales de transresistencia (OTRAs). El modelo se compone de cuatro nullors y tres resistores aterrizados; como resultado, se puede aplicar el análisis nodal estándar para calcular características de pequeña señal completamente simbólicas de circuitos analógicos basados en OTRAs; este nuevo modelo puede ser usado en herramientas CAD. De esta forma, las funciones de transferencia completamente simbólica de varios circuitos de aplicación tales como filtros y osciladores, pueden aproximarse fácilmente.

## 1. Introduction

The operational transresistance amplifier (OTRA) is an important building block in analog integrated circuits [1]-[19]. The reason why circuit designers have focused their attention on it is that the analog signal processing can be extended to highfrequency by using current-mode techniques [1]-[19]. Although the transresistance amplifier is commercially available in bipolar technology, it does not provide a virtual ground at the input terminals and only allow the input current to flow in one direction [3], [5]. On the one hand, recent realizations have been suggested to design OTRAs with CMOS technology [4]-[19]; also, several applications such as instrumentation amplifiers [2], MOSFET-C differentiator [6], integrators [7], continuous-time filters [7], [8], [11], [14], [15], [17], immitance simulators [12], waveform generators multivibrators [13],[18], bistable [16], oscillators [7]-[9] and amplification of signals from current-source transducers [4] have been designed

with OTRAs to overcome the finite gain-bandwidth product associated to Op-amps. Also, both input and output terminals of OTRAs are characterized by low impedance [1]-[19], therefore, all parasitic capacitors associated to these terminals will have little effect on these circuits and the time response limitations incurred by parasitic capacitors should be minimized [11]. On the other hand, OTRA is a high gain current-input voltage-output device which can be considered as a current-to-voltage converter and its behavior can be modeled by using a Current-Controlled Voltage Source (CCVS) and at the same time by using nullors [20]-[49]. By using nullors the behavior of any active device can be modeled [20], [21], [23], [26], [27], [28], [49]; for instance, from new nullor-based models to the first, second and third generation current conveyor along with their inverting equivalents and multiple outputs topologies have been proposed in [27]. Therefore, symbolic analysis techniques can be applied to

approximate small-signal characteristics of OTRAsbased analog circuits [31]-[42].

From the point of view of the symbolic analysis techniques, the Nodal Analysis (NA) method has been widely used to describe networks and it is well know that only NA-compatible elements can be directly introduced into the admittance matrix by using the element stamp method [36]-[40]. This disadvantage has been overcome by using the modified nodal analysis technique in which additional columns and rows are incorporated into the admittance matrix and the non-NA compatible elements are readily included by using stamp [36]-[40]. However, the admittance matrix size depends on the number of node voltages and the branch currents associated to the type of elements contained in the circuit. On the other hand, new stamps associated to the four types of controlled sources as well as the nullors, Op-amps, transistors and impedance converters have been proposed [42]-[46]. The generation of these new stamps is based on the concept of matrix port-equivalence by using infinity-variables [43], [45], Particularly, three circuit models along with their stamps have been proposed for the CCVS and it has been demonstrated that they are identical in the ideal case [43]-[46]. Nevertheless, although they can directly be used in the NA method, the size of the admittance matrix still depends on the number of independent variables. Besides, the stamps associated to the CCVS cannot model completely the behavior of an OTRA since they are only considering one input current, limiting their application to specific circuits where the input current is flowing in one direction.

In this work, a new nullor-based model for the OTRA, which is composed of four nullor and three grounded resistors is reported. As a consequence, the NA method can easily be applied to compute small-signals characteristics of OTRAs-based analog circuits [25]-[32]. The nullor-based model not only reduces the admittance matrix size, if compared with the element stamp method [43], [45], but also analog circuits with both input currents flowing toward the OTRA can easily be analyzed. Therefore, the model proposed can be seen as a behavioral model at the circuit level of abstraction and it is very useful to be used in CAD tools [25], [29], [30], [31], [32], [49]. The paper is organized as follows: in Section 2, the new nullorbased model is deduced by considering the behavior equations of the OTRA along with nullor properties. Section 3 presents the use of this model to calculate symbolic analytical expressions of OTRAs-based filters and oscillators. In this section, the admittance matrix is formulated by using the method introduced in [49]. Finally, the conclusions are given in Section 4.

## 2. Nullor-Based OTRAs-Model

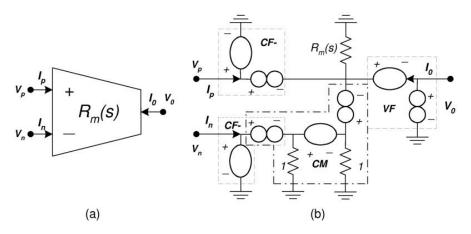

The OTRA shown in Figure 1(a) is a three-terminal analog building block where its input-output terminals are characterized by low impedances [28] and its behavior can be described by

$$\begin{bmatrix} V_p \\ V_n \\ V_0 \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & 0 & 0 \\ R_m(s) & -R_m(s) & 0 \end{bmatrix} \begin{bmatrix} I_p \\ I_n \\ I_0 \end{bmatrix}$$

(1)

Figure 1. (a) OTRA symbol (b) nullor-based OTRA model.

According to the nullor concept and its voltagecurrent relationships, a floating nullator can model very high level impedances [21], [26], [28]-[30]. Contrarily, if any terminal of a nullator is connected to signal-ground, the other terminal is considered as a virtual ground, therefore, a node of lowimpedance is obtained. Furthermore, the voltage across the terminals of a nullator is the same and does not allow current flowing through it. On the other hand, the norator can model both impedance levels: very high or very low, depending on the signal to be measured [21], [26], [28]-[30]. Also, for a norator, a voltage arbitrary can exist across its terminals and the current flowing through it is the same if it is measured in the input-output terminals. According to (1) and Figure 1(a), the output voltage is the difference of the input currents multiplied by the transresistance gain,  $R_m(s)$ , which is ideally infinity; therefore, a change of direction in the flow of In along with external negative feedback must be required to force the input currents to be equal. However, the transresistance gain is finite and its effect along with the frequency limitations associated with the OTRA must be considered. A two-pole model for  $R_m(s)$  is given as

$$R_m(s) = \frac{R_{m0}}{\left(1 + \frac{s}{\omega_{p1}}\right)\left(1 + \frac{s}{\omega_{p2}}\right)} \tag{2}$$

where  $\omega_{p1}$  and  $\omega_{p2}$  are the angular frequencies of the first and second pole and  $R_{m0}$  is the DC gain of the OTRA. Since external negative feedback is required, it is better to design an OTRA with high DC open-loop gain by using bipolar or CMOS transistors [3]-[19]. Therefore, the

behavior of the OTRA in loop-open can adequately be modeled by (2). For middle frequency applications,  $R_m(s)$  can be expressed as

$$R_m(s) \approx \frac{1}{sC_m\left(1+\frac{s}{\omega_{p2}}\right)}; \quad C_m = \frac{1}{R_{m0}\omega_{p1}}$$

(3)

For very high-frequency applications,  $R_m(s)$  can be expressed as

$$R_m(s) \approx \frac{\omega_{p2}}{s^2 C_m} \tag{4}$$

where  $C_m$  is the parasitic capacitance associated to the first pole. On the other hand, since the input impedances of the OTRA are low and only current signals are admitted, they can be modeled with the nullor if one terminal of the nullator is connected to signal-ground and the input current is flowing through the norator. Hence, both input terminals can be modeled with negative current followers (CFs-), as shown in Figure 1(b). For I<sub>n</sub>, it is necessary to invert its direction by using a current mirror, which can be modeled with nullor by using two grounded resistors, as shown in Figure 1(b) [47]-[49]. Note that CFs± are used in the negative/positive input terminals, respectively. To the output terminal, a voltage follower is used, where the current difference is transformed to voltage by  $R_m(s)$ ; this way, the nullor-based OTRA model is shown in Figure 1(b) and it is composed of four nullors and three grounded passive elements, where  $R_m(s)$  can be approximated by (2), (3) or (4). Although the model shown in Figure 1(b) is more complex compared with the nullor-

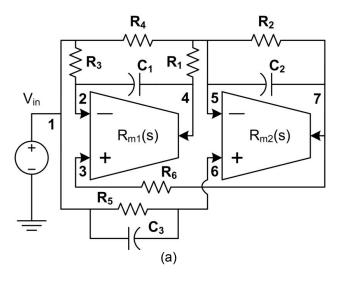

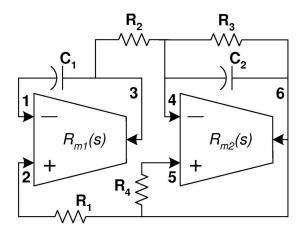

Figure 2. (a) OTRAs-based universal filter (b) nullor equivalent circuit.

based model of a CCVS or the element stamp model [43]-[45], it is more adequate to analyze OTRA-based analog circuits with both input currents flowing toward the OTRA. Besides, the size of the admittance matrix is reduced, as shown in the following sections. It is worth mentioning that the nullor-based OTRA model is adequate to be used in symbolic analysis techniques [25], [26], [29]-[32], [49] since the grounded passive elements have only one entry in the formulation process of the system of equations.

# 3. Symbolic Analysis of OTRAs-Based Filters and Oscillators

As a first example and to show the potentiality of the proposed model, let us consider the universal filter taken from [8], which is depicted in Figure 2(a). The equivalent nullor circuit is shown in Figure 2(b).

In order to compute the fully-symbolic transfer function, the formulation method introduced in [49] is used. In this manner, the system of equations is given by

$$\begin{bmatrix} 0 \\ 0 \\ 0 \\ 0 \\ V_{in} \end{bmatrix} = \begin{bmatrix} -\frac{1}{R_3} & -sC_1 & 0 & 1 & 0 \\ 0 & -\frac{1}{R_{m1}} & -\frac{1}{R_6} & 1 & 0 \\ -\frac{1}{R_4} & -\frac{1}{R_1} & -sC_2 - \frac{1}{R_2} & 0 & 1 \\ -sC_3 - \frac{1}{R_5} & 0 & \frac{1}{R_{m2}} & 0 & 1 \\ 1 & 0 & 0 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_{\{1,16\}} \\ V_{\{4,10\}} \\ V_{\{7,14\}} \\ V_{\{8,9\}} \\ V_{\{12,13\}} \end{bmatrix}$$

(5)

Note that, if the element stamp method is used [43], [45], the size of the admittance matrix is 8×8. By resolving (5) to  $V_{Out}=V_{(7,14)}$ , the fully-symbolic transfer function is given by

$$\frac{V_{Out}}{V_{in}} = \frac{\frac{C_3}{C_2}s^2 + \frac{1}{C_2} \left(\frac{C_3}{R_{m1}C_1} + \frac{1}{R_5} - \frac{1}{R_4}\right)s + \frac{1}{R_{m1}C_1C_2} \left(\frac{1}{R_5} - \frac{1}{R_4}\right) + \frac{1}{R_1R_3C_1C_2}}{s^2 + \left(\frac{1}{R_{m1}C_1} + \frac{1}{R_{m2}C_2} + \frac{1}{R_2C_2}\right)s + \frac{1}{R_{m1}C_1C_2} \left(\frac{1}{R_2} + \frac{1}{R_{m2}}\right) + \frac{1}{R_1R_6C_1C_2}} \tag{6}$$

If (3) is considered, (6) is modified as

$$\frac{V_{Out}}{V_{in}} \approx \frac{\frac{C_{m1}C_3}{C_1C_2\omega_{p2}}s^3 + \left(\frac{C_{m1}}{C_1C_2\omega_{p2}}\left(\frac{1}{R_5} - \frac{1}{R_4}\right) + \frac{C_3}{C_2}\left(1 + \frac{C_{m1}}{C_1}\right)\right)s^2 + \frac{1}{C_2}\left(\frac{1}{R_5} - \frac{1}{R_4}\right)\left(1 + \frac{C_{m1}}{C_1}\right)s + \frac{1}{R_1R_3C_1C_2}}{\frac{C_{m1}C_{m2}}{C_1C_2\omega_{p2}^2}s^4 + \frac{1}{\omega_{p2}}\left(\frac{C_{m1}}{C_1} + \frac{C_{m2}}{C_2} + \frac{2C_{m1}C_{m2}}{C_1C_2}\right)s^3 + \left(1 + \frac{C_{m1}}{C_1} + \frac{C_{m2}}{C_2} + \frac{C_{m1}C_{m2}}{C_1C_2} + \frac{C_{m1}}{C_1C_2R_2\omega_{p2}}\right)s^2 + \frac{1}{R_2C_2}\left(1 + \frac{C_{m1}}{C_1}\right)s + \frac{1}{R_1R_6C_1C_2}}$$

For middle frequency applications:

$$\omega_{p1} \ll |s = j\omega| \ll \omega_{p2}, \ R_{mi} \approx \frac{1}{sC_{mi}}$$

(8)

Therefore, (6) can be approximated to

$$\frac{V_{\text{Out}}}{V_{\text{in}}} \approx \frac{\frac{C_3}{C_2} \left(1 + \frac{C_{\text{m1}}}{C_1}\right) s^2 + \frac{1}{C_2} \left(\frac{1}{R_5} - \frac{1}{R_4}\right) \left(1 + \frac{C_{\text{m1}}}{C_1}\right) s + \frac{1}{R_1 R_3 C_1 C_2}}{\left(1 + \frac{C_{\text{m1}}}{C_1} + \frac{C_{\text{m2}}}{C_2} + \frac{C_{\text{m1}} C_{\text{m2}}}{C_1 C_2}\right) s^2 + \frac{1}{R_2 C_2} \left(1 + \frac{C_{\text{m1}}}{C_1}\right) s + \frac{1}{R_1 R_6 C_1 C_2}}$$

(9)

Therefore,  $\omega_0$  and Q are given by

$$\omega_0 \approx \frac{1}{\sqrt{R_1 R_6 C_1 C_2 \left(1 + \frac{C_{m1}}{C_1} + \frac{C_{m2}}{C_2} + \frac{C_{m1} C_{m2}}{C_1 C_2}\right)}}, Q \approx \frac{R_2 C_1 C_2}{C_1 + C_{m1}} \sqrt{\frac{1 + \frac{C_{m1}}{C_1} + \frac{C_{m2}}{C_2} + \frac{C_{m1} C_{m2}}{C_1 C_2}}{R_1 R_6 C_1 C_2}}$$

(10)

For low frequency,  $C_{m1}$ ,  $C_{m2}$ ,  $\omega_{p1}$  and  $\omega_{p2}$  are insignificant and  $\omega_{0}$  and Q can be approximated to

$$\omega_0 \approx \frac{1}{\sqrt{(R_1 R_6 C_1 C_2)}}, \ \ Q \approx R_2 \sqrt{\frac{C_2}{R_1 R_6 C_1}}$$

(11)

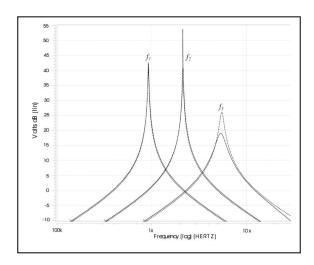

A non-inverting band-pass filter has been designed by using (3), (8), (9) and (10) to give Q=40, where  $R_3=R_4=\infty$ ,  $C_3=0$ ,  $R_1=R_6=1.6k\Omega$ ,  $R_2=80k\Omega$  and  $R_5=800\Omega$  to the following frequencies:  $f_7=0.923$ MHz with  $C_1=C_2=100$ pF and  $f_2=2.12$ MHz with  $C_1=C_2=50$ pF. To  $f_3=5.52$ MHz, we use (3) and

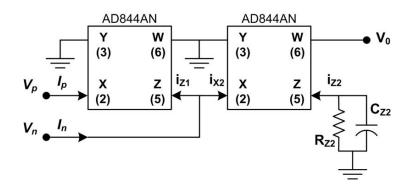

(7) with  $C_1$ = $C_2$ =12pF. To purposes of simulation, the behavior of the OTRA has been modeled with the AD844AN macro-model by using ±5V voltage supply, as shown in Figure 3. However, if the OTRA is designed with CMOS technology, still the model given by (2) and (3) approach well its frequency response.

Figure 3. OTRA implemented with the IC AD844AN.

The angular frequencies associated to the first and second pole along with the DC gain have been approximated of the frequency response of the OTRA; they are given as  $\omega_{p1}$ =69.1krad/s,  $\omega_{p2}$ =95.9Mrad/s and  $R_{mo}$ =127dB. Therefore, by using (3), the numerical values of  $R_{z2}$  and  $C_{z2}$  in Figure. 3 are computed. Comparisons of the bandpass filter magnitude response between HSPICE (Dotted-line) and (9) (Solid-line) for  $f_1$  and  $f_2$ , and by using (7) (Solid-line) for  $f_3$  are shown in Figure. 4, where the symbolic terms are replaced by their numerical values.

From Figure. 4 we can observe that for  $f_1$  and  $f_2$ , the single-pole model given by (8), the transfer function given by (9) and the use of (10), approximate well the frequency response. However to  $f_3$ , the two-pole model given by (3) along with (7) must be used to approximate suitable the magnitude response.

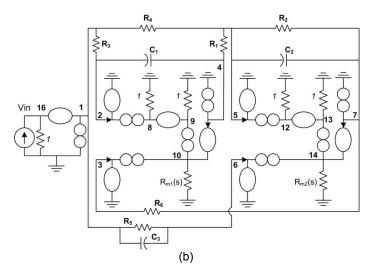

As a second example, lets us consider the OTRAsbased oscillator circuit taken from [9] which is shown in Figure. 5(a). The nullor-based circuit is depicted in Figure. 5(b).

Figure 4. Band-pass magnitude response.

Figure 5. (a) OTRA-based oscillator circuit (b) equivalent nullor circuit.

Again, by using the formulation method proposed in [49], the system of equations is

$$\begin{bmatrix}

0 \\

0 \\

0 \\

0

\end{bmatrix} = \begin{bmatrix}

-sC_1 & 0 & 1 & 0 \\

\frac{1}{R_{m1}} & -\frac{1}{R_1} & 1 & 0 \\

-\frac{1}{R_2} & -sC_2 - \frac{1}{R_3} & 0 & 1 \\

0 & \frac{1}{R_{m2}} - \frac{1}{R_4} & 0 & 1

\end{bmatrix} \begin{bmatrix}

V_{\{3,9\}} \\

V_{\{6,13\}} \\

V_{\{7,8\}} \\

V_{\{11,12\}}

\end{bmatrix}$$

(12)

If element stamp is used [43], [45], the size of the admittance matrix is 6×6. By resolving (12), the characteristic equation is given by

$$s^{2} + \left(\frac{1}{R_{m1}C_{1}} + \frac{1}{R_{m2}C_{2}} + \frac{1}{C_{2}}\left(\frac{1}{R_{3}} - \frac{1}{R_{4}}\right)\right)s + \frac{1}{R_{1}R_{2}C_{1}C_{2}} + \frac{1}{R_{m1}C_{1}C_{2}}\left(\frac{1}{R_{m2}} + \frac{1}{R_{3}} - \frac{1}{R_{4}}\right)$$

(13)

For this case, the single-pole model given by (8) is used. Since  $|s=j\omega| << \omega_{p2}$ , (13) is modified as

$$s^{2} + \frac{1}{C_{2} + C_{m2}} \left( \frac{1}{R_{3}} - \frac{1}{R_{4}} \right) s + \frac{1}{R_{1}R_{2}(C_{1} + C_{m1})(C_{2} + C_{m2})}$$

(14)

Therefore, the condition and frequency of oscillation are given as

$$R_3 = R_4, \qquad \omega_0 = \frac{1}{\sqrt{R_1 R_2 (C_1 + C_{m1})(C_2 + C_{m2})}}$$

(15)

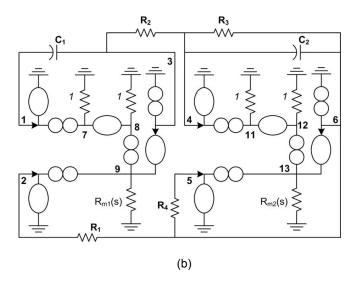

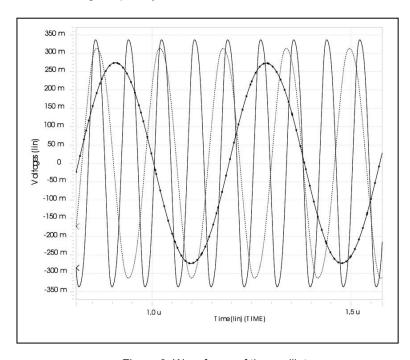

The oscillator of Figure 5(a) was designed and simulated in HSPICE to several frequencies, as shown in Figure 6. By choosing  $R_1=R_2=2k\Omega$ ,  $R_3=R_4=10k\Omega$ , the value of the frequencies of oscillation are found as  $f_1=2.65$ MHz (Dashed-line) with  $C_1=C_2=24$ pF,  $f_2=6.29$ MHz with  $C_1=C_2=6.46$ pF (Dotted-line) and  $f_3=12$ MHz (Solid line) with  $C_1=C_2=0.1$ pF, where the parasitic capacitances have been calculated from (3) and approximated to  $C_{m1}=C_{m2}\approx6.46$ pF. On the other hand, the calculated values of the frequencies of oscillation by using (15) are approximated to  $f_1\approx2.61$ MHz,  $f_2\approx6.16$ MHz and  $f_3\approx12.1$ MHz, which are in close agreement with the simulated results.

From Figure 6, we can observe that the maximum frequency of oscillation ( $f_3$ =12MHz) is limited by  $C_{m1,2}$ = $C_{Z2}$ , according to (8), with  $R_{m0}$ = $R_{Z2}$ , where  $R_{Z2}$  and  $C_{Z2}$  are the parasitic resistance and capacitance associated to the Z terminal of the AD844AN, as shown in Figure 3. It is worth mentioning that the frequency response of the filter can be well approached by using (3), (7), (9) and (10) and it depends on the tuning frequency, while

that for oscillators, the single-pole model given by (8) must be used.

#### 4. Conclusions

We have proposed a new nullor-based OTRAs on computing small-signal focused characteristics of analog circuits. The nullor-based model uses four nullors and three grounded resistors: therefore, a standard nodal analysis can be used and the new model can be included in CAD tools. As examples of the usefulness of the new model, the fully-symbolic transfer function of a non-inverting band-pass filter has approximated, where the one/two-pole model for  $R_m(s)$  has been used to approximate the frequency response of the filter. In the same manner, the condition and frequency of oscillation of an oscillator circuit have been approximated, where the single-pole model associated to  $R_m(s)$  is used; therefore, we can conclude that the nullor-based OTRAs model is quite suitable to compute analytical expressions of OTRAs-based analog circuits.

Figure 6. Waveforms of the oscillator.

#### References

- [1] Brodie J.H. A Notch filter employing current differencing operational amplifier, *Int. J. Electron*, vol. 41, no. 5, pp. 501–508, 1976.

- [2] Agouridis D.C, Fox R.J. Transresistance instrumentation amplifier, *Proc. IEEE*, vol. 66, no. 10, pp. 1286 -1287, 1978.

- [3] National Semiconductors Corp., Designing with a new super fast dual norton amplifier. Linear Applications Data Book, 1981.

- [4] Abidi A. Gigahertz transresistance amplifiers in fine line NMOS, *IEEE* Journal Solid State Circuits, vol. 19, no. 6, pp. 986-994, 1984.

- [5] National Semiconductors Corp., The LM 3900: a new current differencing ± quad of the input amplifiers. Linear Applications Data Book, 1986.

- [6] Chen J, Tsao H, Chen C. Operational transresistance amplifier using CMOS technology. *Electronics Letters*, vol. 28, no. 22, pp. 2087-2088, 1992.

- [7] Salama K.N, Soliman A.M. CMOS operational transresistance amplifier for analog signal processing. *Microelectronics Journal*, vol. 30, no. 3, pp. 235-245, 1999.

- [8] Salama K.N, Soliman A.M. Active RC applications of the operational transresistance amplifier. *Frequenz*, vol. 54, no. 1, pp. 171-176, 2000.

- [9] Salama K.N, Soliman A.M. Novel oscillators using the operational transresistance amplifier. *Microelectronics Journal*, vol. 31, no. 1, pp. 39-47, 2000.

- [10] Barthelemy H. Koudobine I, Landeghem D. Bipolar Low-Power Operational Transresistance Amplifier Based on First Generation Current Conveyor, *IEEE Trans.* on *Circuits and systems II: Analog and Digital Signal Processing*, vol. 48, no. 6, pp. 620-625, 2001.

- [11] Chen J.J, Tsao H.W, Liu S.I. Voltage-mode MOSFET-C filters using operational transresistance amplifier (OTRA's) with reduced parasitic capacitance effect. *IEE Proc. Circuits Devices Syst.*, vol. 148, no. 5, pp. 242-249, 2001.

- [12] Cam U, Kacar F, Cicekoglu O, Kuntman H, Kuntman A. Novel two OTRA-based grounded immitance simulator topologies. *Analog Integrated Circuits and Signal Processing*, vol. 39, no. 2, pp. 169-175, 2004.

- [13] Hou C.L, Chien H.C, Lo Y.K. Square wave generators employing OTRA's. *IEE Proc., Circuits Devices Syst.*, vol. 152, no. 3, pp. 718-722, 2005.

- [14] Cakir C, Cam U, Cicekoglu O. Novel all-pass filter configuration employing single OTRA. *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 52, no. 3, pp. 122-125, 2005.

- [15] Kilinc S, Cam U. Realization of n-th order voltage transfer function using a single operational transresistance amplifier. *ETRI Journal*, vol. 27, no. 5, pp. 647-650, 2005.

- [16] Lo Y.K, Chien H.C. Current-mode monostable multivibrators using OTRAs. *IEEE Transactions on Circuits and Systems II*, vol. 53, no. 11, pp. 1274-1278, 2006.

- [17] Hwang Y.S, Wu D.S, Chen J.J, Shih C.C, Chou W.S. Realization of high-order OTRA-Mosfet-C active filters. *Circuits Systems Signal Processing*, vol. 26, no. 4, pp. 281-291, 2007.

- [18] Lo Y.K, Chien H.C. Switch-controllable OTRA-based square/triangular waveform generator. IEEE *Transactions on Circuits and Systems II*, vol. 54, no. 12, pp. 1110-1114, 2007.

- [19] Lo Y.K, Chien H.C, Chiu H.J. Switch-controllable OTRA-based bistable multivibrators. *IET Circuits Devices Systems*, vol. 2, no. 4, pp. 373-382, 2008.

- [20] Mitra, S. K. Nullator-norator equivalent circuits of linear active elements and their applications. *Proceedings of Asilomar Conference on Circuits and Systems*, pp. 267-276, Pacific Grove USA, November 1-4, 1967.

- [21] Kumar P, Senani R. Bibliography on nullors and their applications in circuit analysis, synthesis and design. *Analog Integrated Circuits and Signal Processing*, vol. 33, no. 1, pp. 65–76, 2002.

- [22] Svoboda JA. Current conveyors, operational amplifiers and nullors. *IEE Proceedings G Circuits, Devices & Systems*, vol. 136, no. 6, pp. 317–322, 1989

- [23] Svoboda JA. Using nullors to analyse linear networks. *International Journal of Circuit Theory and Applications*, vol. 14, no. 3, pp. 169–180, 1986.

- [24] Svoboda JA. Unique solvability of RLC nullor networks. *International Journal of Circuit Theory and Applications*, vol. 11, no. 1, pp. 1–6, 1983.

- [25] Floberg H. Symbolic Analysis in Analog Integrated Circuit Design. Kluwer Academic Publishers, Boston, 1997.

- [26] Tlelo-Cuautle E, Sánchez-López C, Sandoval-Ibarra F. Computing symbolic expressions in analog circuits using nullors. *Computación y Sistemas*, vol. 9, no. 2, pp. 119–132, 2005.

- [27] Tlelo-Cuautle E, Sánchez-López C, Moro-Frías D. Symbolic analysis of (MO)(I)CCI(II)(III)-based analog circuits. *International Journal of Circuit. Theory and Applications*, vol. 38, no. 6 pp. 649-650, 2010.

- [28] Schmid H. Approximating the universal active element. *IEEE Trans on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 47, no. 11, pp. 1160-1169, 2000.

- [29] Sánchez-López C, Tlelo-Cuautle E. Behavioral model generation for symbolic analysis of analog integrated circuits. *IEEE ISSCS*, pp. 327-330, lasi, Romania, July 14-15, 2005.

- [30] Sánchez-López C, Tlelo-Cuautle E. Symbolic behavioral model generation of current-mode analog circuits. *IEEE ISCAS*, pp. 2761-2764, Taipei, Taiwan, May 24-27, 2009.

- [31] Sánchez-López C, Moro-Frías D, Tlelo-Cuautle E. Improving the formulation process of the system of equations of analog circuits, *IEEE SM2ACD*, pp. 102-106, Erfurt, Germany, October 7-8, 2008.

- [32] Tlelo-Cuautle E, Sánchez-López C, Martinez-Romero E, X.-D. Tan S. Symbolic analysis of analog circuits containing voltage mirrors and current mirrors, *Analog Integrated Circuits and Signal Processing*, vol. 65, no. 1, pp 89–95, 2010.

- [33] Tan S. X.-D. Symbolic analysis of analog circuits by Boolean logic operators. *IEEE Trans on Circuits and Systems II: Express Briefs*, vol. 53, no. 11, pp. 1313-1317, 2006.

- [34] Tan S. X.-D, Guo W, Qi Z. Hierarchical approach to exact symbolic analysis of large analog circuits. IEEE Trans on *Computer-Aided Design of Integrated Circuits and Systems*, vol. 24, no. 8, pp. 1241-1250, 2005.

- [35] Doboli A, Vemuri R. A regularity-based hierarchical symbolic analysis method for large-scale analog networks. *IEEE Trans. on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 48, no. 11, pp. 1054–1068, 2001.

- [36] Gielen G, Wambacq P, Sansen W. Symbolic analysis methods and applications for analog circuits: a tutorial overview. *Proceedings of the IEEE*, vol. 82, no. 2, pp. 287–304, 1994.

- [37] Wambacq P, Fernández F.V. Gielen G, Sansen W, Rodríguez-Vázquez A. Algorithm for efficient symbolic analysis of large analogue circuits. *Electronics Letters*, vol. 30, no. 14, pp. 1108–1109, 1994.

- [38] Chua LO, Lin PM. Computer-Aided Analysis of Electronic Circuits: Algorithms and Computational Techniques. Prentice-Hall: Englewood Cliffs, NJ, 1975.

- [39] Gielen GE, Sansen W. Symbolic *Analysis for Automated Design of Analog Integrated Circuits*. Kluwer Academic Publishers, 1991.

- [40] Fernández F.V., Rodríguez-Vázquez A, Huertas JL, Gielen GE. Symbolic Analysis Techniques: Applications to Analog Design Automation. IEEE Press: NY, 1998.

- [41] Shi CJR, Tan XD. Canonical symbolic analysis of large analog circuits with determinant decision diagrams. *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 19, no. 1, pp. 1–18, 2000.

- [42] Sánchez-López C, Fernández F.V, Tlelo-Cuautle E. Generalized Admittance Matrix Models of OTRAs and COAs. *Microelectronics Journal*, vol. 41, no. 8, pp. 502–505, 2010.

- [43] Haigh D.G, Clarke T.J.W, Radmore P.M. Symbolic framework for linear active circuits based on port equivalence using limit variables. *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 53, no. 9, pp. 2011–2024, 2006.

- [44] Haigh D.G. A method of transformation from symbolic transfer function to active-RC circuit by admittance matrix expansion. *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 53, no. 12, pp. 2715–2728, 2006.

- [45] Haigh D.G, Radmore P.M. Admittance matrix models for the nullor using limit variables and their application to circuit design. *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 53, no. 10, pp. 2214–2223, 2006.

- [46] Haigh D.G, Tan F.Q, Papavassiliou C. Systematic synthesis of active-RC circuit building-blocks. *Anal. Integr. Circuits Signal Processing*, vol. 43, no. 3, pp. 297–315, 2005.

- [47] Awad I.A., Soliman A.M. On the voltage mirrors and the current mirrors. *Anal. Integr. Circuits Signal Processing*, vol. 32, no. 1, pp. 79–81, 2002.

- [48] Soliman A.M, Saad R.A. The voltage mirror-current mirror pair as a universal element. *International Journal of Circuit Theory and Applications* 2009; DOI: 10.1002/cta.596

- [49] Sánchez-López C, Fernández F.V, Tlelo-Cuatle E, X.-D. Tan S. Pathological element-based active device models and their application to symbolic analysis, *IEEE Transactions on Circuits and Systems I: Regular papers*, 2011. DOI: 10.1109/TCSI.2010.20097696.

#### **Acknowledgment**

This work has been supported by PROMEP-Mexico under the project number UATLX-PTC-088 and by Consejería de Innovación, Ciencia y Empresa, Junta de Andalucía-Spain, under the project number TIC-2532. The first author thanks the support from the JAE-Doc program of CSIC, cofunded by FSE.

## Authors' Biographies

## Carlos SÁNCHEZ-LÓPEZ

He received the B.S. degree in electronics engineering from Universidad Autónoma de Puebla (BUAP), Mexico, in 1999, and the M.S. and Ph.D. degrees, both in electronics engineering, from the Instituto Nacional de Astrofísica, Óptica y Electrónica (National Institute for Astrophysics, Optics and Electronics), INAOE, Mexico, in 2002 and 2006, respectively. In January 2006, he joined Universidad Autónoma de Tlaxcala (UAT), Mexico, as associate professor and researcher. Since June 2009 he is a postdoctoral research fellow at Instituto Microelectrónico de Sevilla (Microelectronic Institute of Seville), IMSE-CNM, CSIC, Spain. He is a coauthor and author of five book chapters and of more than 70 research journal papers and international proceedings published in the fields of modeling and simulation of linear and nonlinear circuits and systems, chaotic oscillators, symbolic analysis, mixed-signal circuits, RF circuits, and computer-aided circuit design.

## Elyoenai MARTÍNEZ-ROMERO

He received the B.Sc. degree from the Universidad Autónoma de Puebla (BUAP), Mexico, in 2006. and the M.Sc. degree from the Instituto Nacional de Astrofísica , Óptica y Electrónica (National Institute for Astrophysics, Optics and Electronics), INAOE, Mexico, in 2010. His research interests include model order reduction, symbolic analysis techniques and analog circuit design.

## Esteban TLELO-CUAUTLE

Dr. Tlelo-Cuautle received a B.Sc. degree from Instituto Tecnológico de Puebla (ITP), Mexico, in 1993. He then received both the M.Sc. and Ph.D. degrees from Instituto Nacional de Astrofísica , Óptica y Electrónica (National Institute for Astrophysics, Optics and Electronics), INAOE, Mexico, in 1995 and 2000, respectively. Since 2001 he has been a professor-researcher at INAOE. From 2009-2010, he served as a visiting researcher in the Department of Electrical Engineering at the University of California at Riverside, USA. He has authored and co-authored five books, 11 book chapters, 50 journal articles and around 100 conference papers. His research interests include systematic synthesis and behavioral modeling and simulation of linear and nonlinear circuits and systems, chaotic oscillators, symbolic analysis, multi-objective evolutionary algorithms, and analog/RF and mixed-signal design automation tools.