ReCIBE. Revista electrónica de

Computación, Informática Biomédica y

Electrónica

E-ISSN: 2007-5448

recibe@cucei.udg.mx

Universidad de Guadalajara

México

Medina Vázquez, Agustín Santiago; Meda Campaña, María Elena; Gurrola Navarro,

Marco Antonio; Becerra Álvarez, Edwin Christian

Retos Sobre el Modelado del Transistor de Compuerta Flotante de Múltiples Entradas en

Circuitos Integrados

ReCIBE. Revista electrónica de Computación, Informática Biomédica y Electrónica, núm.

1, noviembre, 2012

Universidad de Guadalajara

Guadalajara, México

Disponible en: <http://www.redalyc.org/articulo.oa?id=512251559005>

- ▶ Cómo citar el artículo

- ▶ Número completo

- ▶ Más información del artículo

- ▶ Página de la revista en [redalyc.org](http://redalyc.org)

redalyc.org

Sistema de Información Científica

Red de Revistas Científicas de América Latina, el Caribe, España y Portugal

Proyecto académico sin fines de lucro, desarrollado bajo la iniciativa de acceso abierto

# **Retos Sobre el Modelado del Transistor de Compuerta Flotante de Múltiples Entradas en Circuitos Integrados**

**Agustín Santiago Medina Vázquez**

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara, México

[santiago.mediana@cucei.udg.mx](mailto:santiago.mediana@cucei.udg.mx)

**María Elena Meda Campaña**

Centro Universitario de Ciencias Económico

Administrativas

Universidad de Guadalajara, México

[emeda@cucea.udg.mx](mailto:emeda@cucea.udg.mx)

**Marco Antonio Gurrola Navarro**

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara, México

[marco.gurrolla@cucei.udg.mx](mailto:marco.gurrolla@cucei.udg.mx)

**Edwin Christian Becerra Álvarez**

Centro Universitario de Ciencias Exactas e Ingenierías

Universidad de Guadalajara, México

[edwin.becerra@cucei.udg.mx](mailto:edwin.becerra@cucei.udg.mx)

**Resumen:** En este artículo se presentan las consideraciones que hay que adoptar para el uso del transistor de compuerta flotante de múltiples entradas para el diseño de circuitos integrados analógicos. Para ello se presentan las principales características de este transistor así como sus principales ventajas con respecto al transistor MOSFET convencional que este dispositivo ofrece. También, se exponen los principales problemas que han frenado el uso de este dispositivo en el ámbito comercial debido a la falta de modelos precisos.

**Palabras clave:** CMOS, Analógico, Circuitos, Integrados, Compuerta-flotante, muy bajo voltaje

## 1. Introducción

En la actualidad, los circuitos integrados (Cl's) o chips son elementos electrónicos omnipresentes en cualquier sistema electrónico, tales como sistemas de comunicaciones, cómputo, control, bioelectrónica, metrología, navegación y un largo etcétera. Es sabido que hace un par de décadas los Cl's contaban con solo una decena de transistores, sin embargo, actualmente éstos pueden estar constituidos por millones de ellos. El la gran mayoría de los casos, el transistor más utilizado en la construcción de Cl's es el transistor MOSFET, el cual puede ser de tipo N o de tipo P, lo que da origen a la tecnología de MOSFET Complementado o simplemente tecnología CMOS. La tecnología CMOS permite implementar transistores, capacitores, resistencias, diferentes tipos de diodos, bobinas, y otros interesantes elementos electrónicos con dimensiones inferiores a los micrómetros cuadrados con un mismo proceso de fabricación, lo que permite que todo estos elementos queden integrados en una diminuta pastilla de silicio. Por lo tanto, todo un sistema electrónico puede implementarse sobre esta pastilla de tan sólo un par de milímetros cuadrados de área.

En las últimas dos décadas se dio prioridad a la creación de circuitos integrados digitales, cuyo máximo representante es el microprocesador digital. Sin embargo, en la actualidad se ha generado un gran interés por la creación de circuitos integrados analógicos debido a que éstos otorgan ventajas en el

procesamiento de señales electrónicas que no son posibles en circuitos enteramente digitales. En contraste con el diseño digital, el diseño de CI's analógicos representa un reto interesante debido a que los dispositivos electrónicos involucrados no operan solamente con valores discretos de voltajes y/o corrientes sino que procesan señales continuas que pueden experimentar cambios paulatinos en un intervalo de amplitudes determinadas. Esto ocasiona que el modelado analógico del dispositivo requiera de un enfoque diferente y esto puede ser un proceso más complicado que el modelado digital del mismo. La necesidad de analizar valores continuos conlleva también a la necesidad de modelar dispositivos semiconductores con valores variantes y continuos en un intervalo dado. A pesar de esto, el uso de CI's analógicos ha demostrado ser una alternativa viable para enriquecer el estado del arte de los circuitos integrados en general y particularmente en aquellos circuitos que se requieren estrictamente para el procesamiento de señales continuas.

Por otro lado, otro reto que enfrenta el diseñador de CI's en la actualidad es la creación de circuitos electrónicos operando con voltajes muy pequeños, es decir, inferiores a 1.0 V. Esta es una tendencia vigente dado que el uso de sistemas electrónicos como aquellos que son móviles o que su entorno es de difícil acceso, se encuentra en auge, los cuales son elementos alimentados por baterías o por otras fuentes alternativas de energía que suelen caracterizarse por los bajos niveles de voltajes entregados, como por ejemplo, el caso de las celdas solares. Cuando se trata de sistemas digitales, el bajo voltaje de operación es un problema determinante en circuitos que operan a muy alta velocidad, sin embargo, a bajas velocidades el bajo voltaje de alimentación no es un factor limitante. Sin embargo, en el diseño de circuitos analógicos, el uso de muy bajos voltajes es un reto también interesante debido a que los circuitos generados sufren de la degradación del rango dinámico e indirectamente, en operación a pequeña señal, sufren de la disminución de la frecuencia de operación debido a que las capacitancias involucradas se convierten en un factor determinante. Además, a pesar de que los transistores MOSFET son

cada vez más pequeños, el voltaje de umbral inherente a las uniones metal-semiconductor no disminuyen en la misma proporción y pueden alcanzar valores cercanos a un volt, lo que dificulta la saturación de los transistores con voltajes de compuerta muy pequeños, limitando de nuevo el rango dinámico del transistor operando en forma analógica.

Por otro lado, otro reto que se presenta en el diseño de CI's en general se encuentra en el proceso de simulación por computadora. El comportamiento de todo CI diseñado debe de ser simulado en previamente varias decenas de veces para validar su comportamiento antes de su fabricación real. Esto se debe principalmente a que el prototipado de CI's es un procedimiento muy caro y no se puede seguir una estrategia de prueba y error, sino que el diseñador debe de tener una idea bastante concisa de que su prototipo va a operar de la manera esperada. Esto no era tanto un problema con tecnologías grandes mayores a una micra ya que los modelos de los dispositivos para modelado resultaban ser medianamente sencillos, pero con la llegada de los transistores nanométricos y con la reducción del voltaje de alimentación aparecieron nuevos efectos parásitos los cuales pueden modificar el comportamiento y desempeño de una celda electrónica al grado de obtener resultados completamente indeseados. De esta manera, las ecuaciones que describen el comportamiento de los dispositivos en forma analógica se han vuelto lo bastante complicadas como para requerir el uso de programas de cómputo para su análisis.

Como se ha mencionado ya, el diseño de circuitos integrados analógicos y de muy bajo voltaje de operación es de sumo interés para el desarrollo de una industria basada en el uso de baterías y fuentes de energía alternativas. Existen varias propuestas para obtener circuitos analógicos de bajo voltaje como son el uso técnicas como la denominada auto-cascodo, la técnica de polarización de sustrato, la reducción del voltaje de umbral por procesos químicos, o el uso de nuevas estructuras como los transistores finfets o los transistores de compuerta flotante (Shouli Y. & Sanchez-Sinencio E., 2000;

Prateek Mishra, Anish Muttreja & Niraj K., 2009; E. Sánchez-Sinencio & A. G. Andreau, 1998; S. S. Rajput & S. S. Jamuar, 2002). Cada una de las técnicas propuestas tienen sus propias ventajas y desventajas, por lo que el diseñador debe de elegir la técnica que le proporcionará mejores resultados en cuando a operación en bajo voltaje se refiere. En este artículo abordamos exclusivamente el tema del uso de transistores de compuerta flotante para la creación de circuitos analógicos de muy bajo voltaje de operación

El problema que se discute en este artículo consiste en el uso del transistor de compuerta flotante para el diseño de celdas analógicas de muy bajo voltaje de operación con un modelo confiable para la generación de prototipos de excelente desempeño. Para ello, en las secciones siguientes se muestran las principales características del transistor de compuerta flotante de entrada, se discute el problema principal sobre el modelado del mismo y finalmente se presentan algunas estrategias que se están siguiendo para mejorar el estado del arte sobre el uso de éste interesante dispositivo.

## **2. El Transistor de compuerta flotante de múltiples entradas.**

### **2.1 Voltaje de compuerta flotante**

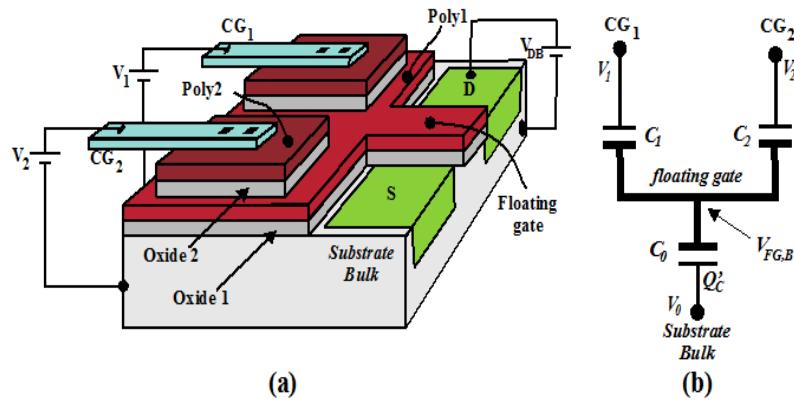

El transistor de compuerta flotante de múltiples entradas (MIFGMOS) (Shibata, T. and Ohmi, T., 1992; Rodriguez-Villegas, E., 2006), se forma con la modificación de un transistor MOSFET convencional como se muestra en la figura 1 (a) .En este caso la compuerta del transistor MOS se rodea de óxido quedando completamente aislada del exterior. Sin embargo, el control de la corriente de drenador a fuente ( $I_{DS}$ ) sigue siendo función del potencial en la compuerta de polisilicio (poly1) del transistor convencional y del potencial en las demás terminales. Sin embargo, en el caso del MIFGMOS es necesario implementar algún mecanismo para inducir voltaje en la compuerta flotante. Se

han propuesto un par de técnicas para conseguir este objetivo los cuales son el uso de técnica de inyección y tuneleo de carga rompiendo el óxido que rodea a la compuerta flotante (Hasler, P., 2001) y la consistente en utilizar solamente el acoplamiento de voltaje a través de capacitores de control, como se muestra en la Figura 1 (a) para el caso de dos compuertas de control. Como puede verse, las compuertas de control  $CG_1$  y  $CG_2$  son conectadas a los voltajes  $V_1$  y  $V_2$ , respectivamente. Estas fuentes se conectan a capacitores formados con capas poly2-oxido-poly1, aunque en algunas tecnologías se pueden implementar con capas metal-oxido-metal. Por todo lo anterior este dispositivo se conoce como transistor de compuerta flotante de múltiples entradas para diferenciarlo de su similar que se controla con técnicas de inyección y tuneleo. En la parte (b) de la figura se muestra el equivalente capacitivo que se genera en la compuerta flotante con respecto al sustrato  $V_{FG,B}$ .

**Figure 1.** (a) Estructura de un transistor de compuerta flotante de dos compuertas de control y (b) divisor capacitivo equivalente de entrada

Así, los voltajes  $V_1$  y  $V_2$  controlarán la cantidad de corriente  $I_{DS}$  que fluye por el transistor desde la fuente hasta el drenador. Cabe mencionar que el MIFGMOS puede tener más de dos compuertas de control, lo que permite que este dispositivo sea más versátil que el MOSFET convencional. En resumen, cuando se aplican  $N$  voltajes de control en  $N$  compuertas de control, en la superficie del sustrato del MOSFET se genera un potencial de superficie como resultado de la suma ponderada de voltajes de entrada que se obtiene de un

divisor capacitivo similar al que se señala en la figura 1 (b). Este potencial de superficie controlará la corriente IDS de manera idéntica al caso de un transistor MOSFET.

Por otro lado, obedeciendo la ley de conservación de carga se obtiene como resultado que el voltaje en la compuerta flotante se puede calcular con la siguiente ecuación [6]:

$$V_{FG,B} = \frac{\sum_{i=1}^N V_i C_i}{C_0 + \sum_{i=1}^N V_i C_i}$$

En donde  $V_i$  son los voltajes de control en las compuertas de control  $CG_i$ , respectivamente y  $C_i$  son los capacitores de acoplamiento.  $C_0$  es la capacitancia entre compuerta y sustrato el cual es de carácter variable y se puede aproximar como el valor de la capacitancia compuerta-sustrato  $C_{GB}$ . En este caso, las demás capacitancias parásitas relacionadas con el sustrato serán desestimadas al considerarse mucho más pequeñas que  $C_{GB}$ .

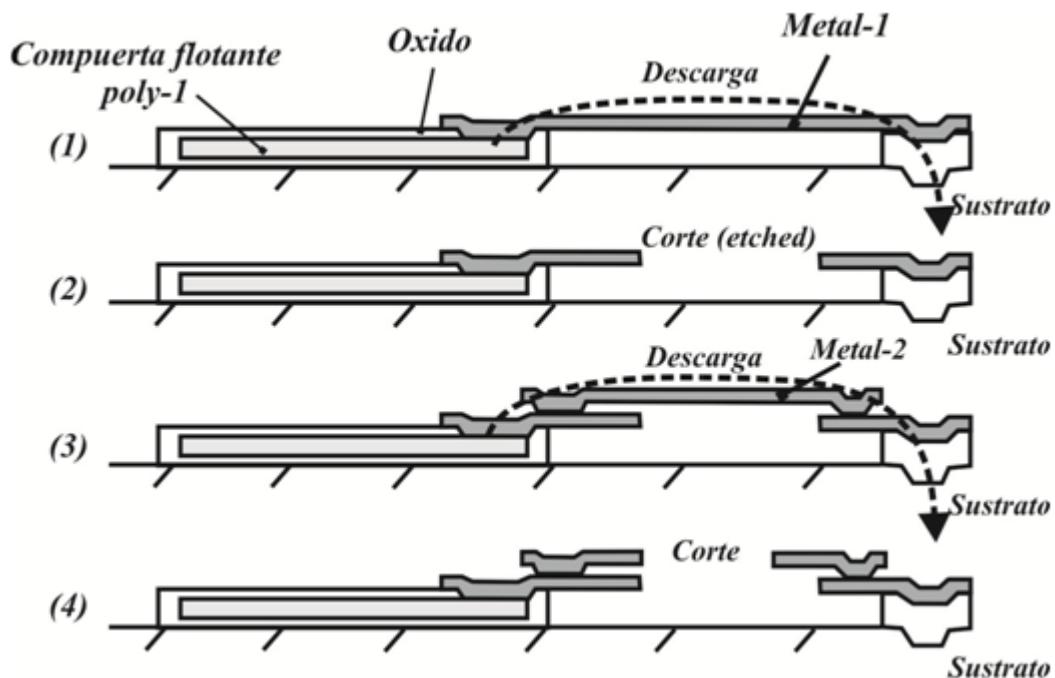

## 2.2 El problema de la carga inicial

Un problema que se presenta con la construcción del MIFGMOS es la presencia de una carga que permanece almacenada involuntariamente en la compuerta flotante desde el proceso de fabricación. Sin embargo, este problema se reduce drásticamente si se utiliza la técnica reportada en (Rodríguez-Villegas, E., 2003). En este caso, se utilizan contactos entre metales para generar un camino de escape a la carga que pretenda quedar atrapada en la compuerta. Como se ve en la Figura 2, por cada capa de metal que se utilice en el diseño, se debe construir un contacto que permita un puente momentáneo entre la compuerta flotante y tierra. La idea principal es

que cuando se haga la deposición de cada metal, se forme un camino a tierra desde la compuerta flotante. Sin embargo, este puente no debe de permanecer, por lo que hay que eliminarlo. Afortunadamente es posible eliminar esta capa de metal manipulando correctamente las máscaras de layout. Este proceso se debe hacer por cada nivel de metal que se utilice, por ejemplo en una tecnología de tres metales se debe de hacer un contacto que haga el puente en cada una de las tres deposiciones de metal.

**Figure 3.** Método de descarga de la compuerta flotante para dos capas de metal por medio de puentes en el proceso de fabricación.

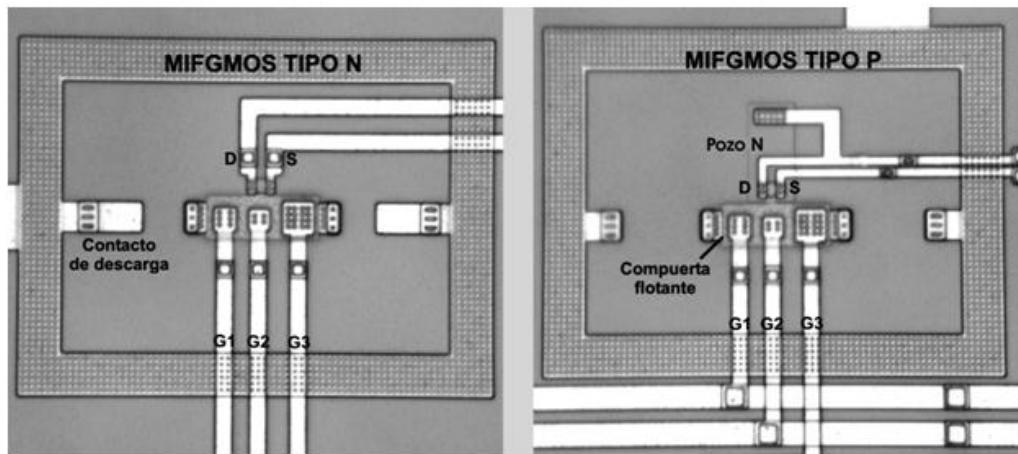

La Figura 3 muestra la implementación de dos transistores MIFGMOS con tres entradas de control, uno de canal N (a la izquierda de la figura) y otro de canal P (a la derecha). Como se indica, se pueden ver los contactos de descarga que permiten eliminar gran parte de la carga en la compuerta flotante durante el proceso de fabricación. Estos dispositivos fueron construidos en una tecnología

de 1.2 micrómetros SCN15 como prototipos de prueba. Se utilizaron anillos de guarda para aislar los dispositivos de prueba del resto de los elementos trazados en el sustrato.

**Figure 3.** Implementación real del MIFGMOS de tres compuertas de control de canal N y de canal P. Se incluye el contacto de descarga

Los parámetros para los transistores MIFGMOS de la Figura 3 se resumen en la Tabla 1.

| Dato  | Valor       | Descripción                 |

|-------|-------------|-----------------------------|

| $C_1$ | 50.1984 fF  | Capacitor de acoplamiento 1 |

| $C_2$ | 40.99536 fF | Capacitor de acoplamiento 2 |

| $C_3$ | 96.63192 fF | Capacitor de acoplamiento 3 |

| $W_n$ | 6.0 um      | Ancho del canal             |

| $L_n$ | 3.6 um      | Largo del canal             |

**Tabla 1.** Parámetros de los transistores mostrados en la Figura 3.

## 2.3 El MIFGMOS para bajo voltaje de operación

El hecho de que el MIFGMOS sea un dispositivo de N entradas de control permite tener algunas ventajas adicionales ante el MOS convencional: (1) Se pueden generar nuevas alternativas y arquitecturas de diseño por el mayor número de grados de libertad y (2) se permite manipular el dispositivo para su utilización con muy bajos voltajes de operación, aun inferiores al voltaje de umbral del MOS convencional. La segunda propiedad es la que nos interesa en este artículo. Existen varios documentos en donde se exponen las ventajas del MIFGMOS en este sentido, sin embargo, en este documento se muestran dos sencillos ejemplos en donde se puede ver la utilidad del MIFGMOS para bajo voltaje (Medina-Vázquez, A., Cruz-Alejo, Gómez-Castañeda, F. & Moreno-Cadenas, J., 2009).

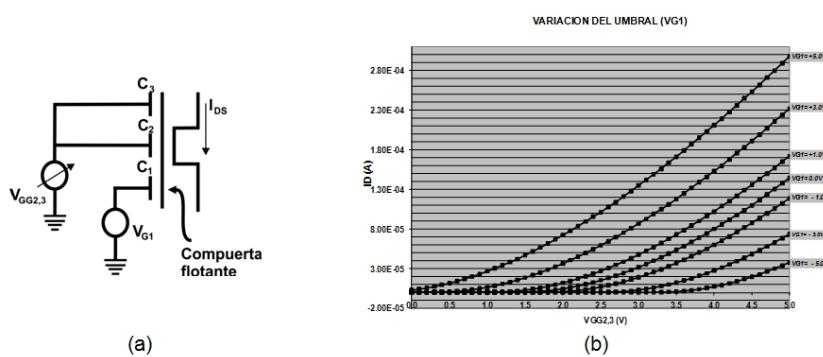

Primero se discute el caso de la manipulación del voltaje de umbral aparente del dispositivo (inicio de conducción del transistor). En realidad, el voltaje de umbral de un MOSFET depende del proceso de fabricación y suele ser un valor fijo que se encuentra cercano a un volt. Sin embargo, si polarizamos el MIFGMOS tipo N de la Figura 3 con la configuración mostrada en la Figura 4 (a) el voltaje de umbral se puede alterar de manera aparente.

**Figure 4.** (a) Circuito de prueba implementado con un MIFGMOS en el laboratorio para observar el fenómeno de voltaje de umbral aparente variable y (b) resultados de las mediciones en donde se muestra la manipulación del voltaje de umbral.

En este caso  $V_{G1}$  se mantiene en un valor fijo de voltaje mientras que la conexión de las entradas de control  $C_{G2}$  y  $C_{G3}$  se unen para que una fuente de voltaje  $V_{GG2,3}$  sea barrida desde 0 a 5 V. La Figura 4 (b) muestra el comportamiento de la corriente  $I_{DS}$  para diferentes valores de  $V_{G1}$ . Como puede verse, el MIFGMOS conduce corrientes con menores voltajes de  $V_{GG2,3}$  conforme  $V_{G1}$  es más grande (también se muestran ejemplos para  $V_{G1}$  negativo). En conclusión, al manipularse el voltaje de umbral del MIFGMOS se pueden obtener valores de corriente  $IDS$  con menores voltajes en las demás compuertas, lo que significa procesamiento con menor voltaje de operación.

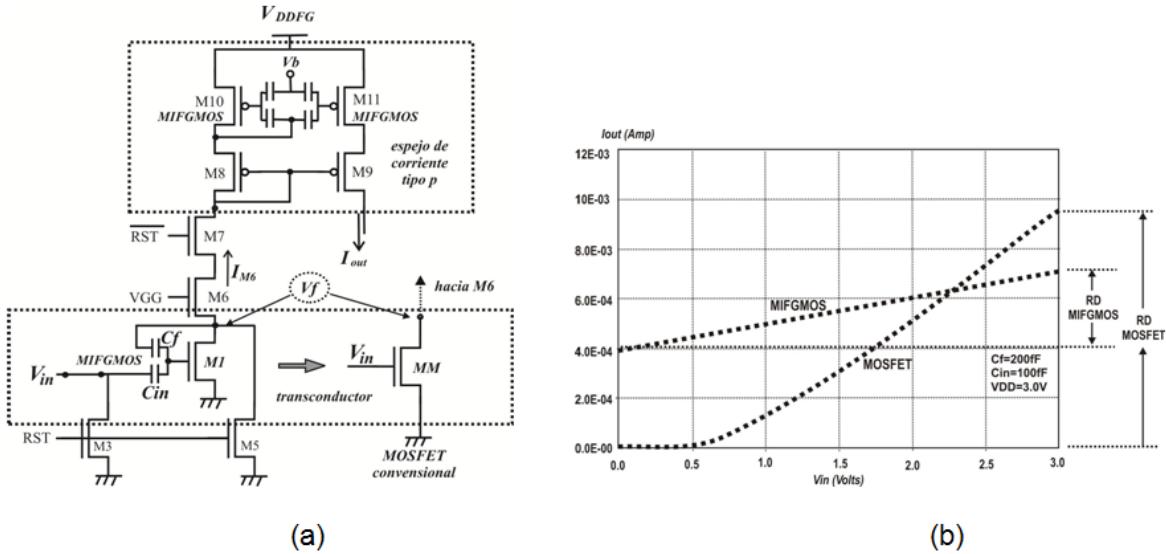

Otra característica del MIFGMOS es que en algunas ocasiones permite mejorar el desempeño de una celda analógica en comparación con el MIFGMOS convencional. Por ejemplo, en la Figura 5 se muestra la implementación de un convertidor de voltaje a corriente (transductor) utilizando un MIFGMOS M1. Como se indica en la figura, este transistor podría ser un MOSFET convencional MM. Sin embargo, la retroalimentación de drenador hacia una de la compuertas de control de M1 por medio del capacitor  $C_f$  permiten mejorar la linealidad del voltaje de salida, como se muestra en la parte (b) de la figura en donde se hace la comparación entre la respuesta que se obtiene si el transductor se construye con un MOSFET convencional o un MIFGMOS.

**Figure 5.** . (a) Transcuctor implementado con MIFGMOS, (b) Comparación de la respuesta de voltaje entre un transductor con MIFGMOS y otro con MOSFET.

### 3. Modelando el MIFGMOS

A pesar de las ventajas que el MIFGMOS puede presentar para el diseño de celdas analógicas de muy bajo voltaje de operación, existen algunos inconvenientes con lo relacionado a la simulación de circuitos que han frenado su uso en forma amplia. Como se ha mencionado previamente, la simulación es una parte fundamental del flujo de diseño y si no se tienen los modelos adecuados, los resultados esperados en los circuitos fabricados pueden llegar a ser inciertos.

Existen varias formas de modelar matemáticamente un transistor MOSFET convencional. Entre los modelos más utilizados se encuentran los siguientes: (1) el modelo de ley cuadrada, (2) el modelo de carga superficial, (c) el modelo EKV y (d) el modelo BSIM. El modelo de ley cuadrada ha sido el más difundido por su sencillez. En este modelo, el comportamiento de la corriente IDS se

modela con dos ecuaciones sencillas, una para la zona de triodo y otra para la zona de saturación y aparece en cualquier libro de texto de diseño de circuitos CMOS (Allen, P., Holberg, D., 2002).

$$I_{DS,triodo} = \frac{K_p}{2} \frac{W}{L} (V_{GS} - V_{th})^2$$

$$I_{DS,saturación} = \frac{K_p}{2} \frac{W}{L} \left[ (V_{GS} - V_{th})V_{DS} - \frac{V_{DS}^2}{2} \right]$$

El modelo de carga superficial (CSM, Charge Sheet Model) es complejo y su característica principal es que modela el comportamiento del MOSFET en todas las zonas de operación (empobrecimiento, inversión débil, moderada y fuerte) por lo que es conocido como modelo toda-región (Yannis Tsividis, 2010). El CSM se forma con un conjunto de ecuaciones basadas en el comportamiento de la distribución de carga en la interface Metal-Oxido-Semiconductor. Este modelo está formado por un conjunto de ecuaciones que describen el comportamiento de la carga superficial y el potencial de superficie  $\psi_S$  que se genera en la zona en donde se forma el canal. Con este modelo se tienen ecuaciones de corriente como las que se muestran a continuación:

$$I_{DS1} = \frac{W}{L} \mu C'_{ox} \left[ (V_{GB} - V_{FB})(\psi_{SL} - \psi_{S0}) - \frac{1}{2}(\psi_{SL}^2 - \psi_{S0}^2) - \frac{2}{3}\gamma(\psi_{SL}^{3/2} - \psi_{S0}^{3/2}) \right]$$

$$I_{DS2} = \frac{W}{L} \mu C'_{ox} [\phi_t(\psi_{SL} - \psi_{S0}) + \gamma(\psi_{SL}^{1/2} - \psi_{S0}^{1/2})]$$

$$I_{DS} = I_{DS1} + I_{DS2}$$

Donde:

$$\psi_{S0} = V_{GB} - V_{FB} - \gamma \sqrt{\psi_{S0} + \phi_t e^{(\psi_{S0} - 2\phi_F - V_{SB})/\phi_t}}$$

$$\psi_{SL} = V_{GB} - V_{FB} - \gamma \sqrt{\psi_{SL} + \phi_t e^{(\psi_{SL} - 2\phi_F - V_{DB})/\phi_t}}$$

Por cuestiones de espacio el significado de estos parámetros no son incluidos en este documento, sin embargo, cada uno de ellos es explicado con profundidad en (Yannis Tsividis, 2010).

Como puede verse, las ecuaciones involucradas suelen ser algo complejas. El sistema de ecuaciones señalado con las ecuaciones (4) - (8) tiene el inconveniente de que para obtener la corriente  $I_{DS}$  primero hay que determinar los valores de los potenciales de superficie  $\psi_{S0}$  y  $\psi_{SL}$  en ambos extremos del canal. Para ello hay que resolver primero las ecuaciones (7) y (8), las cuales deben de ser resueltas por métodos numéricos debido a que son ecuaciones implícitas (la variable no se puede despejar algebraicamente), situación que se ha demostrado que no es del todo fácil, aunque existen muchas soluciones propuestas a este problema.

Otro modelo a considerar para modelar el MOS convencional y al MIFGMOS es el modelo EKV. Este modelo matemático se propuso en principio para su uso en diseño de muy bajo voltaje de operación, situación que con el paso del tiempo se hizo un tópico importante. Este modelo se basa en el uso de un parámetro conocido como voltaje de estrangulamiento o  $V_P$ . Este es un modelo más compacto que el modelo de carga superficial dado que solo cuenta con unas cuantas ecuaciones, unos cuantos parámetros eléctricos y unos cuantos físicos. Por ejemplo, para obtener la corriente  $I_{DS}$  en un transistor con el modelo EKV requerimos de las siguientes ecuaciones:

$$I_{DS} = I_F - I_R$$

donde

$$I_{F(R)} = K\beta\phi_t^2 \exp\left[\frac{V_P - V_{S(D)}}{\phi_t}\right]$$

donde

$$V_P = V_{GS} - VTO - PHI - \gamma' \sqrt{V_{GS} + \left(\frac{\gamma'}{2}\right)^2} - \frac{\gamma'}{2}$$

De nuevo, el significado de los parámetros se explica con detalle en la referencia correspondiente (C. Enz, F. Krummenacher & E. Vittoz, 1995).

Otro modelo que se ha propuesto para el modelado del MOS es el modelo BSIM (William Liu, 2001). En este caso, los resultados se obtienen con ecuaciones basadas de leyes físicas pero también de la experimentación. Muchas de sus ecuaciones son obtenidas por métodos de interpolación y se requieren de algunos parámetros eléctricos y físicos tomados directamente del fabricante.

Todos los modelos presentados previamente son muy importantes para el diseño profesional de circuitos integrados analógicos, pues a partir de ellos se pueden obtener los parámetros físicos y eléctricos que el ingeniero requiere para el diseño de celdas de alto desempeño. Cada modelo tiene sus características propias que lo hacen interesante para una u otra aplicación. Cabe señalar que un modelo no se dirige sólo al cálculo de la corriente  $I_{DS}$  del transistor, sino también a calcular otros fenómenos de segundo orden como son las capacitancias parásitas, la modulación de canal, los fenómenos de segundo orden de canal pequeño, modelo a pequeña señal, etc. Este no es un

tutorial sobre modelos del transistor por lo que se recomienda acudir a los textos señalados en las referencias.

En realidad, para un diseño de alto desempeño existen muchos factores que el diseñador debe de tomar en cuenta y cada modelo de los mencionados aquí permiten modelar estos fenómenos, sin embargo en todos los casos el número de ecuaciones que hay que considerar para obtener un resultado es proceso tedioso y propenso a errores humanos. Por este motivo, se hace necesario el uso de software especializado que resuelva los sistemas de ecuaciones por nosotros. Como es de esperarse, mientras mejor sea el modelo matemáticos utilizados para cada dispositivo que interviene en el circuito, es decir, mientras mejor se apegue el modelo al comportamiento real del dispositivo, se obtendrán mejores resultado en el proceso de simulación.

Para el diseño de circuitos eléctricos en general se utiliza un programa especializado llamado SPICE (Simulation Program with Integrated Circuit Emphasis) (William Liu, 2001). Algunas empresas producen sus propios simuladores basados en el núcleo de SPICE. Las herramientas más socorridas actualmente para el diseño de circuitos eléctricos y de circuitos integrados en particular son las que contiene el ambiente de diseño Cadence, (Virtuoso, Spectre, Allegro, etc.). Este tipo de herramientas de simulación se han refinado para el diseño de circuitos integrados CMOS basados en el modelo de BSIM (aunque hay disponible la posibilidad de utilizar el modelo EKV), al grado que para obtener simulaciones óptimas, la fundidora, el equipo de modelado (por ejemplo la Universidad de Berkeley creadora del modelo BSIM) y la empresa CADENCE trabajan en conjunto en forma continua para procurar los mejores resultados en el proceso de simulación. Se puede considerar que un resultado óptimo en la simulación es aquel que se asemeja notablemente a los resultados que en un futuro se obtendrán en la realidad al hacer mediciones en el laboratorio sobre el objeto físico.

Ahora, cuando se crean circuitos que hacen uso del MIFGMOS se observa una problemática particular, principalmente porque la compuerta flotante del dispositivo es precisamente un punto flotante, es decir, un punto sin referencia. El programa SPICE se encarga de resolver el sistema de ecuaciones matemáticas que resuelven las mallas eléctricas que forman el circuito. Estas ecuaciones a su vez se forman sustituyendo cada dispositivo por el modelo matemático que describe su comportamiento real. Esto genera sistemas de ecuaciones con una gran cantidad de parámetros el cual se debe resolver para una o más variables. Esta es una tarea sencilla para las capacidades de cómputo actuales. Sin embargo el núcleo de programación de SPICE tiene reglas a seguir. Una de ellas es que todos los nodos (interconexión entre dos o más dispositivos) que forman la malla eléctrica deben de estar referenciados a un punto común o tierra, lo que significa que siempre debe de existir algún camino directo o indirecto a través de otros dispositivos para llegar al punto de referencia o tierra. Como es de suponerse, la compuerta flotante queda como un punto o nodo aislado, por lo que esta regla de referencia no se cumple. Como consecuencia, al intentar realizar una simulación con SPICE se obtiene un mensaje de error si se utilizan transistores MIFGMOS. Así, si regresamos a la Figura 4 (a), se puede ver que el nodo de compuerta flotante no tiene ninguna salida al exterior, situación que genera el problema mencionado y por lo tanto no se puede realizar un proceso de simulación para obtener el comportamiento en DC de circuitos con MIFGMOS incluidos. Además, los parámetros en AC del transistor requieren de parámetros obtenidos del análisis DC, por lo que es de suponer que tampoco se podrán obtener resultados de simulación a menos que se apliquen algunos trucos.

Por lo anterior, la simulación de circuitos con MIFGMOS es un problema a resolver. Este problema ha estado presente desde que se propuso el uso de transistores de compuerta flotante un par de décadas atrás, sin embargo, aun hoy no se ha resuelto el problema de manera óptima. De hecho, este transistor sigue siendo utilizado en muchos diseños analógicos pero por lo general no se puede realizar una comprobación del todo confiable con los resultados de

simulación antes de generar el prototipo físico. Esta situación no es muy recomendable dado que la creación de prototipos físicos es muy costoso y el diseñador no debe de exponerse a equivocaciones mayúsculas.

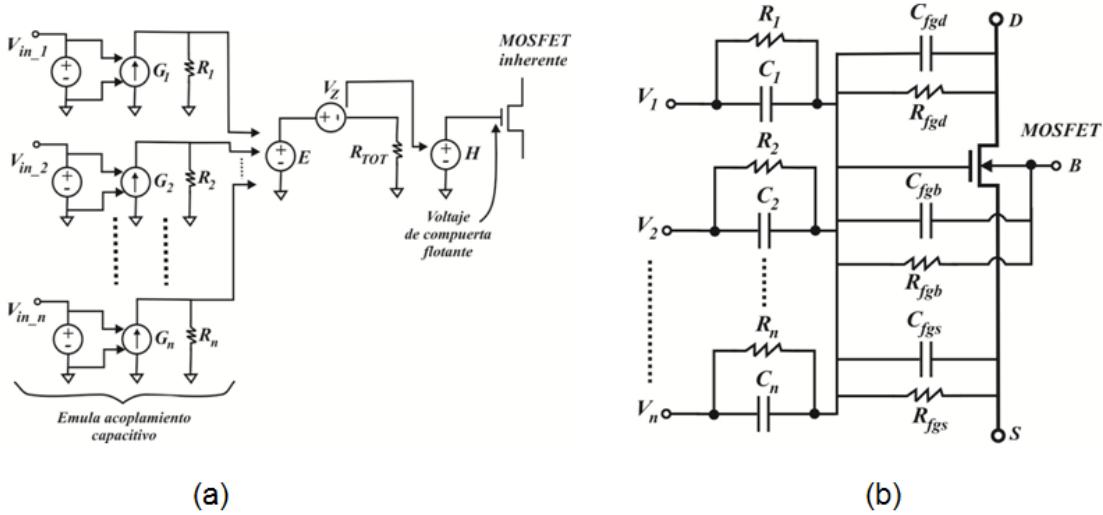

Los primeros intentos para resolver el problema del nodo flotante consistieron en el uso de macro-modelos (Ochiai, T. and Hatano, H., 1999; T. Inoue, H. Nakae, Y. Fukuju & E. Sánchez-Sinencio, 2002). En (Ochiai, T. and Hatano, H., 1999) se propone un macro-modelo en donde el voltaje de compuerta flotante se consigue con la suma de fuentes de voltajes ponderadas por algún valor y con el uso de resistores muy grandes. Esto se muestra en la Figura 6 (a). El problema de este esquema es que estas fuentes de voltaje sólo son un artilugio para implementar la ecuación (1) pero no representan las características reales del dispositivo. Además, algunos parámetros deben de obtenerse manualmente, lo que se aleja de las técnicas modernas de simulación de circuitos. El macromodelo mostrado en la Figura 6 (b) es otra alternativa. Sin embargo, los inconvenientes son similares al macromodelo de la parte (a) de la figura, ya que las capacitancias parásitas deben ser calculadas a mano. Además, las resistencias muy grandes que se utilizan en los macromodelos no están presentes en el circuito real, lo que arroja resultados de simulación basados en dispositivos que ni siquiera existirán en realidad.

**Figure 6.** Ejemplos de dos macromodelos utilizados para modelar el comportamiento del MIFGMOS

Adicionalmente, estos macro-modelos son completamente inútiles para el análisis en AC de celdas analógicas. Así, las incertidumbres que se tienen en el modelado del transistor MIFGMOS han contribuido a que éste no sea utilizado ampliamente, a pesar del potencial que tiene este dispositivo, como se mencionó en secciones previas.

## 4. Nuevas propuestas para el modelado del MIFGMOS

El Laboratorio de Diseño de Circuitos Electrónicos del Centro Universitario de Ciencias Exactas e Ingenierías de la Universidad de Guadalajara está retomando el tema del modelado del transistor MIFGMOS para obtener modelos eficientes de simulación con el objeto de predecir mejor los resultados que se obtendrán en los prototipos reales. Dado que se tienen varios modelos para el MOSFET en general, se ha optado por trabajar inicialmente con el

modelo de carga superficial y con el modelo EKV. El primero de ellos se ha considerado porque es un modelo con muy buenas bases físicas aunque este modelo adolece de ser complejo y de resultados no muy similares a la realidad, sin embargo, proporciona excelentes explicaciones sobre los fenómenos que se están observando en el laboratorio. Por otro lado, el modelo EKV se está utilizando debido a que está en un nivel medio de complejidad y es más fácil de manipular, sobre todo en programas alternativos al SPICE como es el caso de MATLAB.

Las técnicas de simulación que se están explorando se basan en separar el transistor MIFGMOS en dos partes: un transistor MOSFET convencional y una interface capacitiva de entrada (Figura 1 (a)). Dado que la etapa del MOSFET es la misma que un MOSFET convencional los modelos matemáticos permanecen sin cambio sustanciales, pero al añadir la interface capacitiva de entrada, las ecuaciones deben de replantearse. El método radica en sustituir el voltaje de compuerta VGS del MOSFET inherente con valores que se obtienen por separado con ecuaciones que predicen el valor del voltaje con ecuaciones como (1).

El principal problema aparece con las capacitancias parásitas que ahora se deben de considerar en (a) pues estas suelen ser variables conforme varía el voltaje en la compuerta flotante. Por ejemplo, si el voltaje en la compuerta flotante está en función de las capacitancias parásitas ya su vez algunas de estas capacitancias parásitas depende del mismo voltaje en la compuerta flotante, se generarán ecuaciones implícitas que deben resolverse con métodos numéricos. Esto conlleva a buscar el método adecuado para converger a valores correctos, a plantear los valores de las condiciones iniciales de los métodos, entre otros inconvenientes.

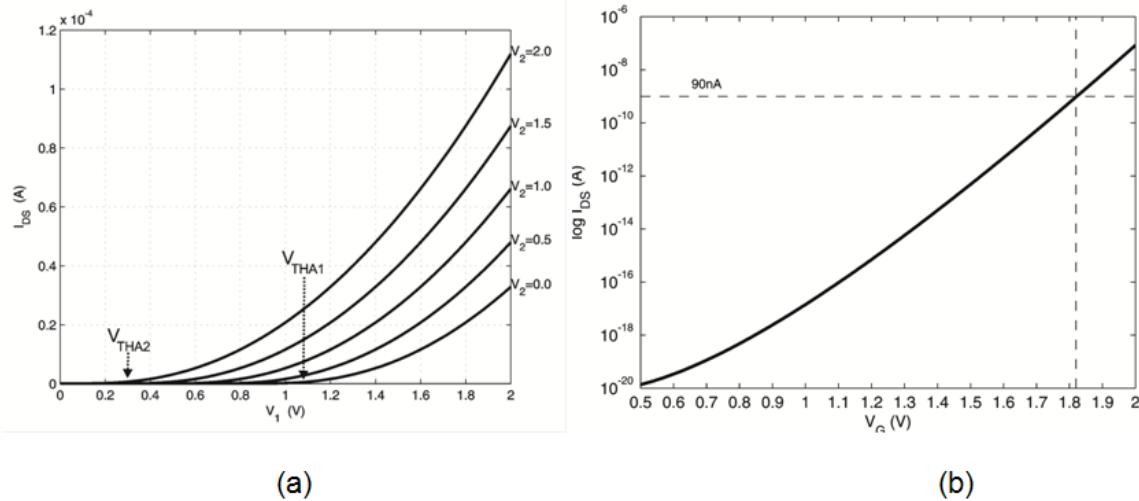

Como ejemplo de los avances que se han realizado ya en el Laboratorio de Diseño de Circuitos, en la Figura 7 se muestra el resultado de utilizar el CSM en una ecuación toda-región. En este caso se tienen dos entradas de control

en donde una de ellas se mantiene fija y la otra experimenta un barrido. Esta gráfica es obtenida en MATLAB resolviendo el sistema de ecuaciones por Newton-Raphson con todos los valores iniciales a cero. Sin embargo, este primer intento adolece de que es necesario mantener fijo el valor de la capacitancia entre la compuerta y el sustrato para no complicar demasiado los métodos a resolver. En la parte (b) se observa otra gráfica de IDS con respecto al voltaje en una de las compuertas de control. De nuevo, una de las compuertas de control se mantiene fija y la otra experimenta un barrido de voltaje. En este ejemplo en particular se ha graficado solamente el comportamiento del MIFGMOS para inversión débil.

**Figure 7.** Algunos resultados obtenidos con el modelaje del MIFGMOS (a) utilizando el CSM y (b) utilizando el modelo EKV en la región de subumbral.

Ambos estudios se están desarrollando en paralelo en donde se ha optado por la estrategia de trazar las curvas en MATLAB para realizar una extracción de parámetro a partir de una familia de gráficas. Estos parámetros permitirán polarizar un MOSFET convencional pero considerando que los potenciales en las compuertas equivalen a los valores deseados en la compuerta flotante.

Junto con el proceso de modelado matemáticos, los resultados deben de ser validados con resultados reales, por lo que parte del proyecto es construir dispositivos FGMOS y celdas basadas en el MIFGMOS para tener mediciones reales y comparar resultados con nuestros métodos. Actualmente estamos entrando a esa segunda etapa.

## 5. Conclusiones

El transistor MIFGMOS tiene un gran potencial para el diseño de celdas de muy bajo voltaje de operación, además de que permite nuevas topologías y estrategias de diseño debido a sus múltiples entradas y a la posibilidad de variar de manera aparente su voltaje de umbral. Sin embargo, es necesario refinar el modelo del dispositivo para obtener resultados de simulación óptimos apegados a la realidad. Para ello se están redefiniendo los modelos utilizando el CSM y el modelo EKV. Cuando se tengan estos modelos, será posible incluirlos en herramientas de simulación basadas en SPICE para obtener resultados confiables.

## References

- Allen, P., Holberg, D. (2002). CMOS Analog Circuit Design. Second Edition. Oxford University Press. Oxford Series in Electrical and Computer Engineering.

- C. Enz, F. Krummenacher and E. Vittoz. (1995). An Analytical MOS Transistor Model Valid in All Regions of Operation and Dedicated to Low-Voltage and Low-Current Applications. Analog Integrated Circuit and Signal Processing. Vol 8. No. 1. pp. 83-114. (2010). Operation and Modeling of the MOS Transistor. Oxford Third Edition. University Press.

- E. Sánchez-Sinencio, A. G. Andreau. (1998). Low-Voltage/Low-Power Integrated Circuits and Systems: Low-Voltage Mixed Signal Circuits. IEEE Solid-State Circuits Society. IEEE Press. ISBN: 0780334469, 9780780334465.

Hasler, P. (2001). Continuous-Time Feedback in Floating-Gate MOS Circuits, IEEE Systems-II: Analog and Digital Signal Processing, Vol. 48, No. 1, pp. 56 – 64.

Medina-Vázquez, A., Cruz-Alejo, Gómez-Castañeda, F., Moreno-Cadenas, J. (2009). Low-voltage linear transconductor and a memory current using the MIFGMOS Transistor. Vol. 96, No. 9, September 2009, 895 - 914.

Ochiai, T. and Hatano, H. (1999). A Proposition on Floating Gate Neuron MOS Macromodeling for Device Fabrications. IEICE Trans. Fundamentals, Vol. E82-A, No. 11, pp. 2485 – 2491.

Prateek Mishra, Anish Muttreja and Niraj K. (2009). Low-power FinFET circuit synthesis using multiple supply and threshold voltages. ACM Journal on Emerging Technologies in Computing Systems (JETC). Vol. 5. Issue 2. Article 7.

Rodriguez-Villegas, E. (2003). Solution to trapped Charge in FGMOS Transistors, Electronics Letters, Volume 39, Issue 19, pp. 1416 – 1417.

Rodriguez-Villegas, E. (2006). Low Power and Low-Voltage Circuit Design with the FGMOS Transistor, London, United Kingdom. The Institution of Engineering and Technology.

Shibata, T. and Ohmi, T. (1992). "A Functional MOS Transistor Featuring Gate-Level Weighted Sum and Threshold Operations". IEEE Transactions on Electron Devices, Vol. 39, Issue 6, pp. 1444-1455.

Shouli Y. and Sanchez-Sinencio E. (2000), Low Voltage Analog Circuit Design Techniques: A tutorial. IEICE Transactions on Analog Integrated Circuits and Systems, Vol. E00-A. No 2.

S. S. Rajput, S. S. Jamuar. (2002). Low Voltage Analog Circuit Design Techniques. IEEE Systems and Circuits Magazine. Vol. 2, issue 1, pp. 24 – 42.

T. Inoue, H. Nakae, Y. Fukuju y E. Sánchez-Sinencio. (2002). A Design of a Low-Voltage Current-Mode Fully-Differential Analog CMOS integrator Using FG-MOSFET and Its Implementation. Analog Integrated Circuits and Signal Processing. Vol. 32. Issue 3. Pp. 249 – 256.

William Liu (2001). MOSFET Models for SPICE Simulation Including BSIM3v3 and BSIM4. John Wiley and Sons Inc. ISBN: 0-471-39697-4

Yannis Tsividis (2010). Operation and Modeling of the MOS Transistor. Oxford Third Edition. University Press. Allen, P., Holberg, D. (2002). CMOS Analog Circuit Design. Second Edition. Oxford University Press. Oxford Series in Electrical and Computer Engineering.

## Biographical notes:

**Dr. Austin Santiago Medina Vazquez** received the Bachelor degree on Communications and Electronics Engineering from the University of Campeche, Mexico in 1999, the Master degree on Telecommunications in 2003 in CINVESTAV Guadalajara, and the Doctoral degree on Science, with speciality on Integrated Circuit Design, from the CINVESTAV Zacatenco in 2009. Since 2009 he is working in the University of Guadalajara and his current research interests are mixed signal integrated circuit design. Nowadays, his main project is based in modelling and implementation of very low power integrated circuit based on the floating gate transistor.

**Dr. María Elena Meda** has received her PhD in electronic engineering in 2002 at the Research Center and Advanced Studies of the National Polytechnic Institute, Mexico. Since 2003 she works at the University of Guadalajara as a full time professor at the Information System Department. Her main research area is the modeling and applications of discrete event systems (DES) based on interpreted Petri nets (IPN).

**Dr. Marco A. Gurrola-Navarro** received the Bachelor degree on Communications and Electronics Engineering from the University of Guadalajara, Mexico in 1997, the Master degree on Earth Sciences from the University of Guadalajara, 2003, and the Doctoral degree on Science, with speciality on Integrated Circuit Design, from the National Institute of Astrophysics Optics and Electronics, at Tonantzintla, Mexico in 2009. Since 2009 he is working in the University of Guadalajara and his current research interests are mixed signal integrated circuit design, and SoC.

**Dr. Edwin Christian Becerra Alvarez** received the B.S. degree on Communications and Electronic Engineering from the University of Guadalajara, Mexico in 2004, the M.S. degree on Electric Engineering from CINVESTAV, Mexico in 2006 and the Ph.D. degree on Microelectronics from the University of Seville, Spain in 2010. Since 2010 he is working in the University of Guadalajara and his current research interests are on CMOS RF circuits.

Esta obra está bajo una licencia de Creative Commons

Reconocimiento-NoComercial-CompartirIgual 2.5 México.