Jimenez Moreno, Robinson; Aviles Sanchez, Oscar; Ramos Sandoval, Olga Lucía

ANÁLISIS DE LA IMPLEMENTACIÓN DE UN CONTROLADOR DIFUSO SOBRE DIFERENTES

ARQUITECTURAS DE HARDWARE.

Ciencia e Ingeniería Neogranadina, vol. 23, núm. 1, junio, 2013, pp. 77-87

Universidad Militar Nueva Granada

Bogotá, Colombia

Disponible en: <http://www.redalyc.org/articulo.oa?id=91129721005>

- ▶ Cómo citar el artículo

- ▶ Número completo

- ▶ Más información del artículo

- ▶ Página de la revista en [redalyc.org](http://redalyc.org)

# ANÁLISIS DE LA IMPLEMENTACIÓN DE UN CONTROLADOR DIFUSO SOBRE DIFERENTES ARQUITECTURAS DE HARDWARE.

## IMPLEMENTATION ANALYSIS OF A FUZZY CONTROLLER OVER DIFFERENT HARDWARE TOOLS

Robinson Jiménez Moreno

Ingeniero Electrónico, M.Sc. Profesor, Investigador GAV

Universidad Militar Nueva Granada, Bogotá, Colombia

[robinson.jimenez@unimilitar.edu.co](mailto:robinson.jimenez@unimilitar.edu.co)

Oscar Aviles Sánchez

Ingeniero Electrónico, Ph.D. Profesor, Investigador DAVINCI

Universidad Militar Nueva Granada Bogotá, Colombia

[oscar.aviles@unimilitar.edu.co](mailto:oscar.aviles@unimilitar.edu.co)

Olga Lucía Ramos Sandoval

Ingeniero Electrónico, M.Sc. Profesora

Universidad Militar Nueva Granada, Bogotá, Colombia

[olga.ramos@unimilitar.edu.co](mailto:olga.ramos@unimilitar.edu.co)

Fecha de recepción: 27 de noviembre de 2012

Fecha de aprobación: 10 de mayo de 2013

### RESUMEN

Este artículo compara el desempeño de tres arquitecturas microcontroladas en la implementación de un controlador difuso, las cuales corresponden a un PIC18F2550, un MSP430G2452 y un DSPIC30F4011. Con el objetivo de establecer cuál de ellas ofrece una ventaja o desventaja en términos de la memoria utilizada, tanto de programa como de datos, tiempo de respuesta y potencia consumida. Permitiendo de esta forma establecer las características de cada una de ellas y criterios claros para la selección de alguna, en una aplicación de control embebida y en general cualquier aplicación

que exija del dispositivo capacidad de almacenamiento y velocidad de procesamiento.

**Palabras claves:** comparación de arquitecturas, controlador difuso, memoria de programa, microcontrolador.

### ABSTRACT

This paper compares the performance of three micro-controlled architectures in the implementation of a fuzzy controller, these correspond to a PIC18F2550, a MSP430G2452 and DSPIC30F4011. In order to establish which of them offers

an advantage or disadvantage in terms of memory used for both program and data, response time and power consumption. Thus allowing setting the characteristics of each and criteria for selecting one in an embedded control application and in general any application that requires the device storage capacity and processing speed.

**Keywords:** comparison of architectures, fuzzy controller, microcontroller, program memory.

## 1. INTRODUCCIÓN

Hoy día, en la implementación de diversas aplicaciones referentes a controladores digitales, es posible conseguir desarrollos de una gran variedad de fabricantes. Entre estos se encuentran las arquitecturas microcontroladas, con las cuales es posible solucionar los requerimientos de la electrónica digital. A nivel de ingeniería, muchas investigaciones utilizan microcontroladores para implementar la parte de control, es así como en [1] se diseña un sistema de control de acceso por medio de un microcontrolador de la familia ATMega16. En [2] se diseña un sistema educativo para enseñanza de microcontroladores en función a un microcontrolador Freescale MC9S12C32. En [3] se presenta el diseño de un controlador discreto PID con microcontrolador, sin especificar la referencia o familia utilizada. En [4] se emplea un microcontrolador ARM Cotex-M3 para el diseño e implementación de una unidad terminal remota o RTU, en un sistema de automatización. En [5] se presenta el diseño de una lengua elec-

trónica por medio de un microcontrolador PIC18F4550, utilizando algoritmos de inteligencia artificial, en este caso lógica difusa y redes neuronales.

Con respecto a esta última aplicación entre los esquemas de control hoy día, cobran fuerza los implementados mediante sistemas difusos, ya que permiten establecer el diseño del controlador, para el control de una planta lineal o no, mediante una serie de reglas que describen el comportamiento del mismo. En [6] se presenta un sistema de control de nivel basado en lógica difusa y aplicado a un arreglo de tres tanques, utilizando a la vez técnicas de procesamiento de imagen. En [7] se presenta el desarrollo de un controlador PID clásico mejorado, mediante la acción en paralelo de un controlador difuso. En [8] se presenta el diseño de un controlador difuso para el control de nivel de un tanque en un sistema de caldera. En [9] se desarrollan algoritmos de inferencia difusa para un controlador de tráfico vehicular.

En los diferentes trabajos relacionados, se encuentra que los sistemas difusos son implementados o en un equipo de computo o en un dispositivo microcontrolado. No se presenta una relación frente a las características de hardware requeridas, solo en [10] se encontró una comparación básica de algunas arquitecturas de microcontroladores, a fin de desarrollar un sensor de red inalámbrico bajo el agua. Los demás casos mencionados abordan la implementación de la electrónica digital por medio de una referencia específica de microcontrolador, sin ahondar en por qué o el cómo fue es

## ANÁLISIS DE LA IMPLEMENTACIÓN DE UN CONTROLADOR DIFUSO SOBRE DIFERENTES ARQUITECTURAS DE HARDWARE

escogida dicha referencia. Debido a esto, en el presente artículo se desarrolla un controlador difuso implementado en diferentes arquitecturas de hardware, como son: un microcontrolador MSP430G2452 de Texas Instruments (TI), un microcontrolador 18f2550 de Microchip y un dsPIC30f4012 de la misma marca, a fin de poder comparar el desempeño de cada uno de ellos, las ventajas y desventajas que ofrecen, entorno a una aplicación de control de nivel mediante un sistema difuso.

Dichas referencias obedecen a las encontradas en varios artículos del estado del arte y a su vez a la intención de comparar no solo dos arquitecturas de diferente fabricante, sino dos arquitecturas diferentes, del mismo fabricante y tener así mayores elementos de juicio a la hora de concluir. Es de aclarar que estas referencias son a su vez comerciales y relativamente económicas dentro de lo ofrecido en mercado relacionado.

En adelante el documento está organizado de la siguiente forma: en la Sección 2 se describe el diseño del controlador difuso a implementar, en la Sección 3 se describe las características básicas de las tres arquitecturas a comparar y el algoritmo del controlador utilizado, en la Sección 4 se presenta el análisis de resultados y finalmente en la Sección 5 las conclusiones.

### 2. CONTROLADOR DIFUSO

La selección del controlador difuso obedece a dos características fundamentales en

la implementación de un sistema de control de nivel, la primera es el que permite el diseño del controlador sin necesidad de establecer un modelo matemático riguroso del sistema, lo cual está fuera del interés de este trabajo. Por otro lado, aunque el modelamiento de un sistema basado en un único tanque no es difícil, el utilizar técnicas de control clásico derivaría en un controlador digital, que comparado con el difuso no genera una fuerte carga computacional, aspecto fundamental para la comparación de las arquitecturas deseadas.

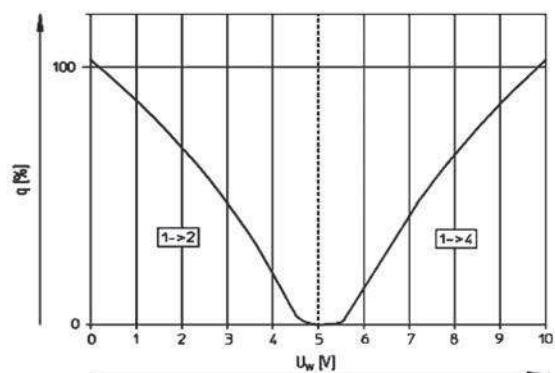

El diseño del controlador difuso está enmarcado en un sistema de control de nivel cuyo actuador es una electroválvula de llenado y desagüe del tipo proporcional FESTO MPYE, la cual opera en el rango de 0 a 5 voltios, para máximo y mínimo caudal respectivamente, como se aprecia en la figura 1.

Figura 1. Diagrama V-Q válvula proporcional.

La respuesta de la válvula permite inferir la forma de las funciones de pertenencia a utilizar y el universo de discurso de salida ( $V_i$ ), el cual se establece en correspondencia con la acción de control. Para este caso, dicha acción de control corresponde a una

señal PWM generada por el microcontrolador a utilizar, con un ciclo útil dado en porcentaje (0-100), a fin de generar el rango de voltaje de operación de la válvula.

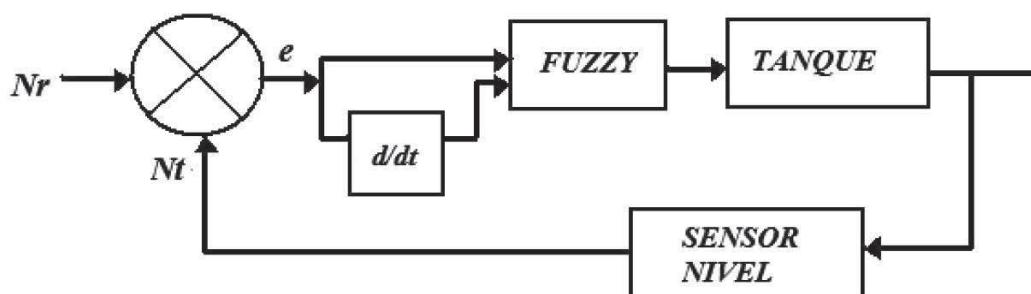

La figura 2 muestra el esquema de control a utilizar, el sensor de nivel corresponde a un sensor ultrasónico de referencia PEPPERL-FUCHS UB8010-18GM40-I-V1, el

cual toma mediadas en el rango de 50 a 800 mm con una resolución de 0,4 mm. Las entradas del controlador difuso están determinadas por la diferencia entre el nivel deseado en el tanque ( $N_r$ ) y el nivel medido en un instante  $k$  ( $N_t$ ), y la razón de cambio de dicha diferencia, Es decir, el error de nivel y su derivada, como se indica la ecuación 1.

Figura 2. Lazo de control

$$\begin{aligned} e(k) &= N_r - N_t \\ \frac{de}{dt} &= e(k) - e(k-1) \end{aligned} \quad (1)$$

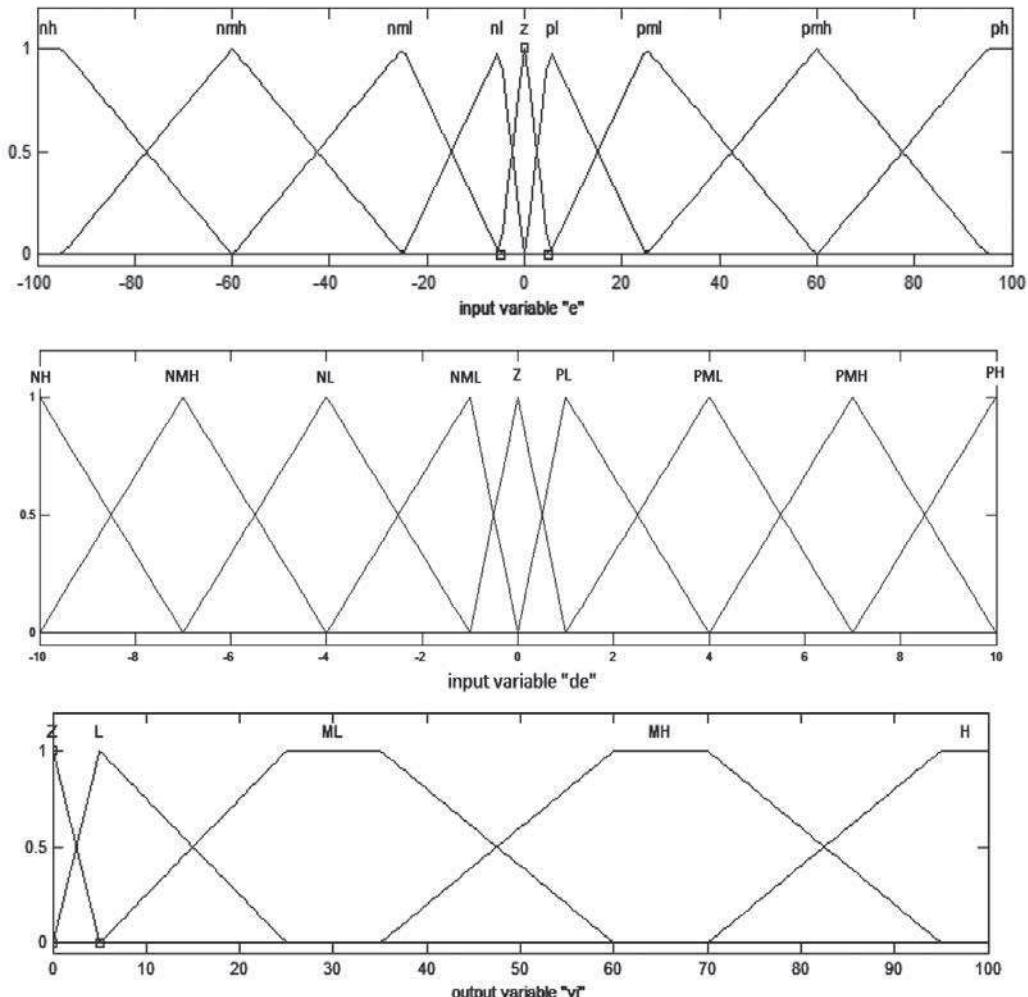

Debido a que se busca generar una cierta carga computacional, se requiere un número considerable de funciones de pertenencia. Típicamente, se encuentra que en el diseño de controladores difusos, al error se le asignan etiquetas lingüísticas de "cero", "bajo", "medio" y "alto", sin embargo para aumentar los requerimientos de almacenamiento del microcontrolador y aumentar el tiempo de procesamiento requerido, se divide la etiqueta "medio" en dos, "medio alto" y "medio bajo". Dado que el error puede ser positivo o negativo se generan cuatro condiciones derivadas de esta etiqueta, aumentando así de 49 reglas de inferencia a 81.

El conjunto difuso que caracteriza la entrada del error y su derivada es:

$$e = de = \{ph, pmh, pml, pl, z, nl, nml, nmh, nh\}$$

donde  $e$  se encuentra en el rango

$$e = \{-100, \dots, 0, \dots, 100\}$$

Debido a la naturaleza "lenta" del sistema de nivel, la variación del error es pequeña, por lo que el conjunto difuso de se establece en el rango  $de = \{-10, \dots, 0, \dots, 10\}$ . Para la salida, respecto a la señal de control de la válvula, se tiene el conjunto difuso  $Vi = \{L, ML, MH, H\}$  en el rango  $Vi = \{0, \dots, 100\}$ . Donde en cada caso  $p$  representa positivo,  $n$  a negativo,  $h$  a alto,  $m$  a medio,  $l$  a bajo y  $z$  a cero, por ejemplo  $ph$  corresponde a error positivo alto. En la figura 3 se ilustra cada uno de los conjuntos difusos definidos.

## ANÁLISIS DE LA IMPLEMENTACIÓN DE UN CONTROLADOR DIFUSO SOBRE DIFERENTES ARQUITECTURAS DE HARDWARE

**Figura 3.** Conjuntos difusos del controlador.

La forma de las funciones de pertenencia de dichos conjuntos difusos, tanto de entrada como de salida, se derivan de la acción deseada para el comportamiento del sistema de control de nivel y se relacionan con la forma de accionado de la válvula (Fig 1). Por ejemplo se observa que tanto para el error como para el delta del error, en los conjuntos de entrada, la función de pertenencia triangular que caracteriza el cero (*z*) tiene una base reducida, lo cual está orientado a asegurar un error de estado estacionario cero en el nivel final del tanque. Por consiguiente, cada función de pertenencia permite una acción de llenado o vaciado gradual, según el incremento del error y su derivada. Bajo esta misma lógica, el que las funciones de pertenencia *ph* y *nh*, del conjunto del error sean trapezoidales, asegura una acción de apertura máxima de llenado o vaciado, a fin de disminuir el tiempo de respuesta del sistema.

tado a asegurar un error de estado estacionario cero en el nivel final del tanque. Por consiguiente, cada función de pertenencia permite una acción de llenado o vaciado gradual, según el incremento del error y su derivada. Bajo esta misma lógica, el que las funciones de pertenencia *ph* y *nh*, del conjunto del error sean trapezoidales, asegura una acción de apertura máxima de llenado o vaciado, a fin de disminuir el tiempo de respuesta del sistema.

Otra característica de los conjuntos difusos definidos es que, para cualquier valor de entrada se tendrá una pertenencia total igual a uno (1) en las funciones de pertenencia dentro de cada universo de discurso

(Ruspini). La base de reglas de activación para el controlador difuso se muestra en la Tabla 1. El método de defuzzyfación utilizado corresponde al centro de gravedad (COG), el cual se muestra en la ecuación 2.

**Tabla 1.** Base de reglas del controlador.

| de\ne | NH | NMH | NML | NL | Z  | PL | PML | PMH | PH |

|-------|----|-----|-----|----|----|----|-----|-----|----|

| NH    | H  | H   | MH  | MH | ML | ML | L   | L   | Z  |

| NMH   | H  | MH  | MH  | ML | ML | L  | L   | Z   | L  |

| NML   | MH | MH  | ML  | ML | L  | L  | Z   | L   | L  |

| NL    | MH | ML  | ML  | L  | L  | Z  | L   | L   | ML |

| Z     | ML | ML  | L   | L  | Z  | L  | L   | ML  | ML |

| PL    | ML | L   | L   | Z  | L  | L  | ML  | ML  | MH |

| PML   | L  | L   | Z   | L  | L  | ML | ML  | MH  | MH |

| PMH   | L  | Z   | L   | L  | ML | ML | MH  | MH  | H  |

| PH    | Z  | L   | L   | ML | ML | MH | MH  | H   | H  |

$$y' = \frac{\sum_{j=1}^F \mu_{B'}(y_j) \cdot y_j}{\sum_{j=1}^F \mu_{B'}(y_j)} \quad (2)$$

Este método de defuzzyfación permite que el resultado obtenido, para una activación de reglas determinada, cubra la mayor parte del universo de discurso de salida, para el caso del COG se tiene del 1,3 al 97,8 por ciento, mientras que otros métodos convencionales como el medio de los máximos MOM, permite obtener del 2,3 al 95,4 por ciento.

### 3. ARQUITECTURAS IMPLEMENTADAS

Las arquitecturas escogidas obedecen a referencias de fácil adquisición y de uso común en el desarrollo de sistemas microcontrolados, con características base como son: encapsulado tipo PDIP, 20-28 pines de conexión, puertos de entrada/salida digital y canales de conversión análogo digital de 10 bits de resolución. Para el caso y bajo estas características se emplean: un microcontrolador MSP430G2452 de Texas Instruments, un microcontrolador 18f2550 de Microchip y un DSPIC30f4012 de este mismo fabricante. La Tabla 2 muestra una relación de las características principales de cada una de estas arquitecturas.

## ANÁLISIS DE LA IMPLEMENTACIÓN DE UN CONTROLADOR DIFUSO SOBRE DIFERENTES ARQUITECTURAS DE HARDWARE

**Tabla 2.** Características de las arquitecturas escogidas.

| Característica     | MSP430G2452   | 18f2550   | DSPIC30f4012 |

|--------------------|---------------|-----------|--------------|

| Tiemp X instr. min | 62.5ns        | 100ns     | 50ns         |

| Memor. Program     | 8KB           | 16KB      | 16KB         |

| Memor. Datos.      | 256B          | 2KB       | 2KB          |

| PWM                | no            | si        | si           |

| Bus de Datos       | 16            | 8         | 16           |

| Puertos I/O        | 16            | 24        | 20           |

| Canales analog.    | 10            | 8         | 6            |

| Compilador C       | Code Composer | Mplab c18 | Mplab c30    |

Los criterios de evaluación que dan lugar a la comparación de estos tres microcontroladores, son: cuanto espacio en memoria de programa utiliza cada uno, este parámetro está asociado al compilador de C que usan. Cuanto espacio de la memoria de datos ocupa, lo cual depende del bus de datos y la compilación, en este caso se tiene un gran uso de esta debido al alto número de reglas generadas en el diseño del controlador, en este caso 81 reglas en total. Finalmente se tiene el tiempo de procesamiento, parámetro para el cual todos los dispositivos usan un oscilador de 10 MHz.

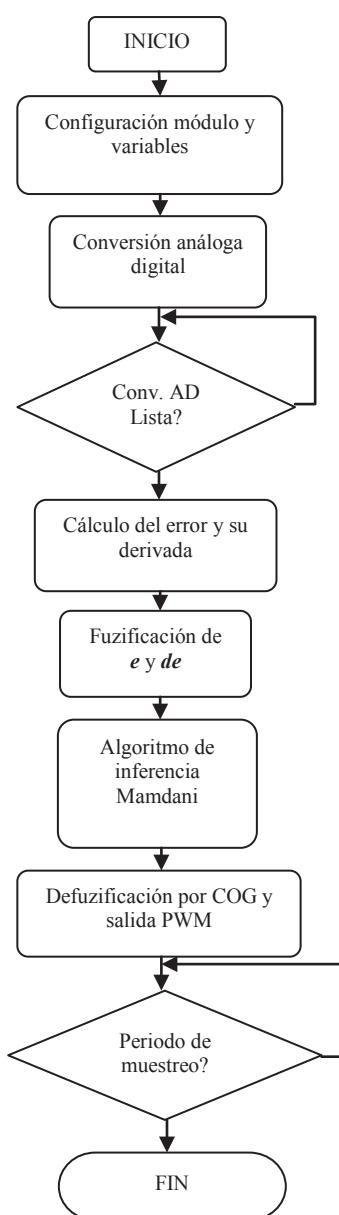

Para la programación del controlador difuso diseñado en cada una de las arquitecturas escogidas, se utiliza el algoritmo de inferencia Mamdani presentado en [11] y el cual se muestra en la figura 4. De forma tal que el programa general se desarrolla en relación al código en lenguaje C propio de cada arquitectura y su compilador. En la figura 5 se presenta el diagrama de flujo general para la programación de los microcontroladores, respecto al esquema de control establecido.

1. Compute the degree of fulfillment for each rule by:  $\beta_i = \max_X [\mu_{A'_i}(X) \Lambda \mu_{A_2}(X)]$ ,  $1 \leq i \leq K$ . Note that for a singleton set ( $\mu_{A'_i}(X) = 1$  for  $X = X_0$  and  $\mu_{A'_i}(X) = 0$  otherwise) the equation for  $\beta_i$  simplifies to  $\beta_i = \mu_{A'_i}(X_0)$ .

2. Derive the output fuzzy sets  $B'_i : \mu_{B'_i}(y) = \beta_i \Lambda \mu_{B_i}(y), y \in Y, 1 \leq i \leq K$ .

3. Aggregate the output fuzzy sets  $B'_i : \mu_{B'_i}(y) = \max_{1 \leq i \leq K} \mu_{B'_i}(y), y \in Y$ .

**Figura 4.** Algoritmo de inferencia Mamdani

El código, según el diagrama de flujo, inicia estableciendo las variables y configuración de puertos y periféricos propios de cada arquitectura. Se debe adquirir el valor correspondiente al nivel actual del tanque,

Figura 5. Diagrama de flujo del algoritmo general.

por medio de una conversión análogo-digital, la cual una vez realizada permite calcular tanto el error actual como su derivada, dado un nivel de referencia. Teniendo estos parámetros se procede a fusificarlos, obteniendo el valor del ciclo útil de la señal PWM que acciona la válvula, después de aplicado el algoritmo de inferencia mamdani y su respectiva defuzzyfación. Dicha labor se realiza periódicamente para actualizar el valor de apertura/cierre de la válvula según la acción de control.

#### 4. ANÁLISIS DE RESULTADOS

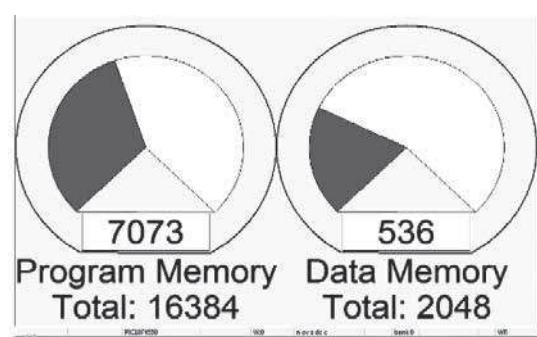

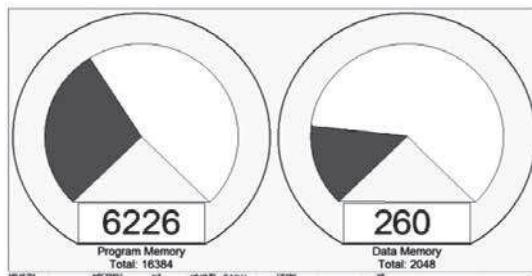

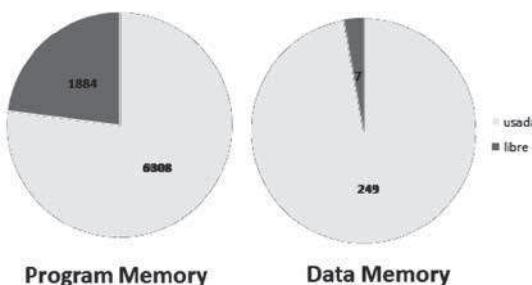

La ejecución del código mostrado en el diagrama de flujo de la figura 5, presentó una carga en la memoria de programa y de datos para cada arquitectura como se muestra en las figuras 6 a 8. La variación en el uso de la memoria de programa está directamente ligada a como el compilador de C genera el código en lenguaje de máquina, para lo cual algunos son más eficientes que otros, por ejemplo para el caso de las dos arquitecturas de Microchip se utilizó una versión gratuita que no está orienta a maximizar la eficiencia en dicha tarea.

Figura 6. Uso de memoria PIC18f2550

## ANÁLISIS DE LA IMPLEMENTACIÓN DE UN CONTROLADOR DIFUSO SOBRE DIFERENTES ARQUITECTURAS DE HARDWARE

Figura 7. Uso de memoria DSPIC30F4012

Figura 8. Uso de memoria MSP430G2452

Se observa que el dspic ocupa menor espacio en memoria, pero no muy diferente al utilizado por el micro de TI, sin embargo en cuanto a memoria de datos se invierten los papeles. En este último caso, da a lugar la consideración de la capacidad de memoria del micro de TI, ya que no es muy amplia y como se evidencia en la figura 8 se usa casi completamente, lo que limita la cantidad de reglas o funciones adicionales con las que se podría mejorar la respuesta del controlador implementado. La diferencia notable en cuanto a memoria de datos encontrada en el pic18f2550, obedece a la cantidad de bits del bus de datos que para este es de 8, mientras para las dos anteriores es de 16, si tomamos este punto de referencia dicho micro estaría utilizando 268 Bytes, un valor aún por encima de las dos arquitecturas previas mencionadas.

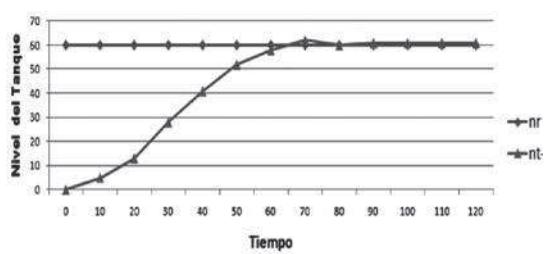

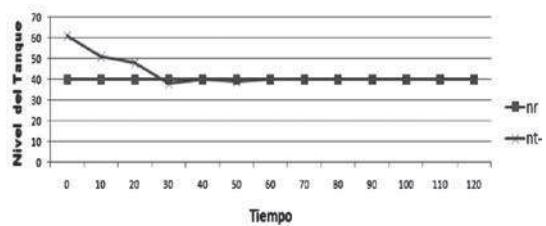

La Figura 9 y 10 muestra la respuesta final del sistema de control de nivel, en la primera cuando la referencia está por encima del nivel actual del tanque y la segunda cuando está por debajo. Debido a que en el sistema se establece un tiempo de muestreo de 1 segundo, la respuesta final de control es la misma para cada arquitectura, por lo que solo se observa una única curva de respuesta en la variable del nivel del tanque ( $N_t$ ). Sin embargo en función al tiempo de ejecución por instrucción de cada arquitectura y la cantidad de memoria de programa utilizada se puede inferir el tiempo de procesamiento. En la Tabla 3 se establece un estimado del tiempo de ejecución del algoritmo, donde se observa que este es menor en el micro de TI.

Tabla 3. Tiempos de ejecución del algoritmo base.

|                     | MSP430G2452 | 18f2550  | DSPIC30f4012 |

|---------------------|-------------|----------|--------------|

| Tiempo de ejecución | 2,2 mseg    | 2,8 mseg | 2,5 mseg     |

Figura 9. Respuesta temporal en llenado del tanque

Figura 10. Respuesta temporal en desagüe del tanque

De forma general, la respuesta del controlador es adecuada en términos del caudal que maneja la electro válvula y la respuesta de las arquitecturas microcontroladas. El error de estado estacionario es cero en cada caso y la división de la etiqueta lingüística "medio" empleada genera mayor tiempo de apertura de la válvula, ayudando a la reducción del tiempo de asentamiento.

## 5. CONCLUSIONES

Se logró implementar un algoritmo de control difuso, orientado a un sistema de control de nivel, el cual generó un requerimiento considerable, tanto de memoria como de tiempo de ejecución, en la programación de las tres arquitecturas de hardware escogidas, permitiendo así realizar una comparación general del desempeño de cada una.

La selección de una arquitectura específica, para dar solución a un requerimiento por medio de un sistema microcontrolado, depende en gran medida de la aplicación. Para el caso particular de un controlador difuso, los resultados obtenidos para el microcontrolador MSP430G2452, se muestran superiores a las dos arquitecturas de Microchip, que aun cuando no es considerable la mejora ofrecida, sobresale dentro del marco experimental establecido. En contraparte la arquitectura de esta referencia en particular de TI, se encuentra en los límites necesarios para el desarrollo del algoritmo, inconveniente no presentado en las otras dos y el cual afectaría un mejora en la respuesta del mismo.

Para la aplicación de un sistema de control de nivel, se evidencio que los tiempos de respuesta del microncontrolador no son considerables, dada la naturaleza "lenta", en relación al tiempo de procesamiento, de la aplicación. Por lo tanto, en estos casos prima la capacidad de memoria y módulos periféricos. Aunque el microcontrolador de TI utilizado no posee un periférico de PWM interno, a diferencia de los de Microchip, el implementarlo con temporizadores no presentó una carga adicional de procesamiento.

## 6. BIBLIOGRAFÍA

- [1] Horvat, G.; Sostaric, D.; Zagar, D., "User authorization system using ZigBee WSN and AVR architecture," Telecommunications Forum (TELFOR), 2011 19th , vol., no., pp.381-384, 22-24 Nov. 2011.

- [2] Deaky, B.; Lupulescu, N.B.; Ursutiu, D.; , "Extended educational use of the Microcontroller Student Learning Kit (MCU SLK)," Global Engineering Education Conference (EDUCON), 2011 IEEE , vol., no., pp.913-916, 4-6 April 2011.

- [3] Zul Azfar, A.; Hazry, D.; , "A simple approach on implementing IMU sensor fusion in PID controller for stabilizing quadrotor flight control," Signal Processing and its Applications (CSPA), 2011 IEEE 7th International Colloquium on , vol., no., pp.28-32, 4-6 March 2011.

- [4] Hong-Chan Chang; Li-Chien Huang; Cheng-Chuan Chen; Cheng-Chein Kuo; "Design and implementation of remote terminal unit for feeder automation system with high performance microcontroller," Industrial Electronics and Applications (ICIEA), 2011 6th IEEE Conference on , vol., no., pp.382-386, 21-23 June 2011.

## ANÁLISIS DE LA IMPLEMENTACIÓN DE UN CONTROLADOR DIFUSO SOBRE DIFERENTES ARQUITECTURAS DE HARDWARE

- [5] Garcia-Breijo, E.; Atkinson, J.; Garrigues, J.; Gil, L.; Ibanez, J.; Glanc, M.; Olguin, C.; , "An electronic tongue for monitoring drinking waters using a fuzzy ARTMAP neural network implemented on a microcontroller," Industrial Electronics (ISIE), 2011 IEEE International Symposium on , vol., no., pp.1270-1275, 27-30 June 2011.

- [6] Jimenez Moreno Robinson, Aviles Sanchez Oscar, Espinosa Fabio, "Level measurement comparison between 3D vision system based on Kinect and ultrasonic industrial sensor". Asian Transactions On Engineering ISSN: 2221-4267 ed: v.2 fasc.5 p.10 - 19 ,2012

- [7] Li Liang; "The application of fuzzy PID controller in coupled-tank liquid-level control system," Electronics, Communications and Control (ICECC), 2011 International Conference on , vol., no., pp.2894-2897, 9-11 Sept. 2011.

- [8] Zhuo Wang; Qiang Wang; , "Application of fuzzy controller in drum water-level control," Mechatronic Science, Electric Engineering and Computer (MEC), 2011 International Conference on, vol., no., pp.174-176, 19-22 Aug. 2011.

- [9] Jimenez Moreno Robinson, Aviles Sanchez Oscar, Espinosa Fabio y Gordillo, Camilo. "Machine Vision algorithms applied to dynamic traffic light control". Revista Dyna ISSN: 0012-7353 ed: Universidad Nacional de Colombia, v.80 fasc.180 p.56 - ,2013.

- [10] Sanchez, A.; Blanc, S.; Yuste, P.; Serrano, J.J.; "A low cost and high efficient acoustic modem for underwater sensor networks," OCEANS, 2011 IEEE - Spain , vol., no., pp.1-10, 6-9 June 2011.

- [11] Babuska Robert, "Fuzzy and Neural Control DISC Course Lecture notes". Delft University of Technology. Sept 2004.