Superficies y vacío

ISSN: 1665-3521

alex@fis.cinvestav.mx

Sociedad Mexicana de Ciencia y Tecnología de Superficies y Materiales A.C.

México

Chung, C.K.; Jaw, T.H.; Wuu, D. S.; Hwang, J.

Electrical properties of Ir-silicide formation on p-Si(100) in ultra high vacuum

Superficies y vacío, núm. 9, diciembre, 1999, pp. 177-179

Sociedad Mexicana de Ciencia y Tecnología de Superficies y Materiales A.C.

Distrito Federal, México

Available in: http://www.redalyc.org/articulo.oa?id=94200947

Complete issue

More information about this article

Journal's homepage in redalyc.org

Scientific Information System

Network of Scientific Journals from Latin America, the Caribbean, Spain and Portugal Non-profit academic project, developed under the open access initiative

# Electrical properties of Ir-silicide formation on p-Si(100) in ultra high vacuum

C.K. Chung, T.H. Jaw, and D.S. Wuu Microsystems Laboratory, Industrial Technology Research Institute, Chutung, Hsinchu, Taiwan 310, R.O.C.

### J. Hwang

Department of Material Science and Engineering, National Tsing Hua University, Hsinchu, Taiwan 300, R.O.C.

An epitaxial Ir-silicide film was grown on the top of p-Si(100) substrate at high temperature of 450 °C in ultra high vacuum. The epitaxial Ir-silicide film was identified to be  $Ir_3Si_4$  with four types of epitaxial modes. The average Schottky barrier height of the epitaxial  $Ir_3Si_4/p$ -Si(100) diode at 60-100K was determined to be 0.177 eV with an ideality factor of 1.12. In contrast, a polycrytalline IrSi/p-Si(100) diode was formed by conventional room-temperature deposition and annealing at high temperatures, and its average Schottky barrier height was 0.157 eV with an ideality factor of 1.08. The difference in Schottky barrier height was attributed to the difference of phase composition and microstructure between  $Ir_3Si_4$  and IrSi silicides.

Keywords: epitaxial, Ir-silicide, ideality factor, Schottky barrier height, ultra high vacuum

#### 1. Introduction

Ir-silicide/p-Si(100) Schottky barrier infrared detectors have received much attention and are also potentially usefully for 8-12 µm infrared charge coupled device (IRCCD) imager arrays [1-4]. In genearl, Ir is deposited on a p-Si(100) substrate in high vacuum (a base pressure of 10<sup>-6</sup>- 10<sup>-7</sup> Torr), then annealed at 350- 500 °C, either in nitrogen [1] or in vacuum [2-4], in order to form IrSi/p-Si Schottky contact. One of the fundamental issues in Schottky contacts is the effect of interface microstructure on the Schottky barrier height. Pellegrini et al. [5] reported that the thermal Schottky barrier height is 0.216 eV for PtSi/p-Si(100) and 0.292 eV for PtSi/p-Si(111).

The difference in atomic arrangement at the interface results in a 0.076 eV difference in Schottky barrier height.

The microstructure of silicide can also affect the Schottky barrier height of silicide/Si contacts. Tung [6] reported that the Schottky barrier height of NiSi<sub>2</sub>/Si(11) was 0.65 eV for type A NiSi<sub>2</sub> and 0.79 eV for type B. In our previous work, we successfully grew the epitaxial  $\rm Ir_3Si_4$  phase on a Si(100) substrate at 450-475 °C in ultra high vacuum (a base pressure of  $10^{-10}$  Torr) [7-9]. In comparison, we also grew the polycrystalline IrSi phase on Si(100) by conventional room temperature deposition of Ir then annealed at 475 °C in ultra high vacuum [8]. It is of much interest to examine the effect of microstructure difference on the electric properties of Ir-silicide/p-Si(100) Schottky contacts.

In this paper, the electric properties of polycrytalline and epitaxial Ir-silicide/p-Si(100) Schottky didodes are investigated. The Schottky barrier height of Ir-silicide/p-Si(100) contacts is measured by using the current-voltage (I-V) method at 60-100K. The average

Schottky barrier height at 60-100K is determined to be 0.177 eV for the epitaxial  $\text{Ir}_3\text{Si}_4/\text{p-Si}(100)$  contact, which is 0.02 eV higher than that for the polycrytalline IrSi/p-Si(100) contact.

#### 2. Experimental

The boron doped p-Si(100) wafers with a resistivity of 25- 35  $\Omega$ m were cleaned by the Ishizaki and Shiraki method [10]. A thin thermal oxide of 4000 Å was grown at 900 °C on both sides of a wafer. The backside oxide was then removed by 6:1 BOE solution for ion implantation.

A low resistance of Al/p+-Si ohmic contact was ensured by implanting the backside of wafers with 30 keV  $BF_2^+$  to a dose of 1 x  $10^{15}$  cm<sup>-2</sup>. The wafers were annealed at 1000 for 15 sec in a rapid thermal annealing (RTA) chamber in order to activate the implanted boron. The area of diodes was defined to be circles of 1 mm in diameter by standard photolithography and etching techniques. The wafers were loaded into an ULVAC electron gun deposition chamber at a base pressure of 10<sup>-10</sup> Torr and then heated at 900 °C for 30 min in order to remove the native oxide before deposition. The epitaxial Ir<sub>3</sub>Si<sub>4</sub>/p-Si(100) Schottky diode was prepared by depositing and annealing pure Ir films of 100 Å on the ascleaned Si(100) substrates at 450 °C due to its smooth interface while the polycrystalline IrSi/p-Si(100) Schottky diode was formed by room temperature deposition of Ir of 100 Å then annealed at 450 °C for 1.5 hour in ultra high vacuum [8, 9].

The I-V characterizations of the Ir-silicide/p-Si(100) Schottky diodes were measured at low temperatures of 40-  $200~\rm K$  with a Keithley model  $230~\rm K$

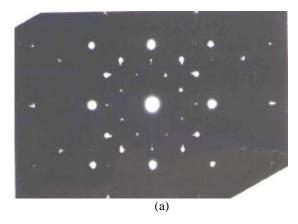

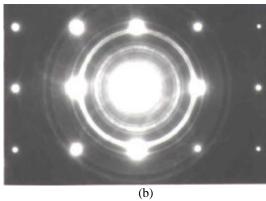

Fig. 1 Transmission electron diffraction patterns of: (a) epitaxial  $Ir_3Si_4$  and (b) polycrytalline IrSi on p-Si(100) substrate.

programmable voltage source and a Keithley model 670 digital electrometer. The diodes were directly attached to the copper plate on the helium cold head in a cryorefrigerator to improve the accuracy of temperature measurement. The temperature was calibrated by using a silicon diode sensor directly attached on the copper plate. The Schottky barrier height and ideality factor was determined by extrapolating the forward current-voltage characteristic to zero applied voltage.

## 3. Results and Discussion

Figs. 1(a) shows the transmission electron diffraction (TED) pattern of Ir-silicide formed on p-Si(100) by depositing and annealing pure Ir at 450 °C in ultra high vacuum. The spotty pattern indicates that the Ir-silicide is epitaxial and identified to be  $Ir_3Si_4$  with four epitaxial modes [7]. The I-V characteristics of the epitaxial  $Ir_3Si_4/p\text{-Si}(100)$  contact at temperatures of 60-100 K are shown in Fig. 2. The corresponding zero biased Schottky barrier heights  $(\varphi_{b0})$  and ideality factors (n) are listed in Table I. The linear regions of the I-V curves at 60-80 K are over approximately four order of magnitudes. The barrier height  $\varphi_{b0}$  increases from 0.168 eV at 60 K with n value of 1.19 to 0.179 eV at 100 K with n value of 1.10. The temperature dependence of  $\varphi_{b0}$  and n is due to the

Fig. 2 I-V characteristics of the epitaxial  $Ir_3Si_4/p$ -Si(100) diode at temperatures of 60-100 K.

interfacial states at the  $Ir_3Si_4/p$ -Si(100) interface. The reliable average  $\varphi_{b0}$  is determined to be 0.177 eV with an ideality factor of 1.12.

Figs. 1(b) shows the TED pattern of Ir-silicide prepared by room temperature deposition of Ir then annealed at 450 °C for 1.5 hour in ultra high vacuum. The ring pattern indicates that the Ir-silicide is polycrytalline and identified to be IrSi [8]. The I-V characteristics of the polycrytalline IrSi/p-Si(100) contact at temperatures of 60-100 K are shown in Fig. 3. The corresponding  $\phi_{b0}$  and n value are listed in Table II. Similarly, the linear regions of the I-V curves at 60-80 K are still over approximately four order of magnitudes. The  $\phi_{b0}$  increases from 0.155 eV at 60 K with n value of 1.10 to 0.159 eV at 100 K with n value of 1.07. The reliable average  $\phi_{b0}$  is determined to be 0.157 eV with an ideality factor of 1.08. In comparison to epitaxial Ir<sub>3</sub>Si<sub>4</sub>/p-Si(100) diode, the barrier heights of polycrytalline IrSi/p-Si(100) diode with better n value of 1.08 is 0.02 eV lower than that for the epitaxial IrSi/p-Si(100) with n of 1.12. The difference in Schottky barrier heights is attributed to the atomic arrangement difference at the Irsilicide/p-Si(100) interfaces. The atomic arrangement

Table I. Schottky barrier heights and ideality factors of the epitaxial  ${\rm Ir}_3{\rm Si}_4/{\rm p\text{-}Si}(100)$  diode at different temperatures

| Temperature | Barrier height    | Ideality factor |

|-------------|-------------------|-----------------|

| (K)         | $(\phi_{b0}, eV)$ | (n)             |

| 60          | 1.19              | 0.168           |

| 70          | 1.12              | 0.176           |

| 80          | 1.12              | 0.177           |

| 90          | 1.11              | 0.178           |

| 100         | 1.10              | 0.179           |

Fig. 3  $\,$  I-V characteristics of the polycrytalline IrSi/p-Si(100) diode at temperatures of 60-100 K.

difference is from two approachs: phase composition and microstructure.

The epitaxial Ir<sub>3</sub>Si<sub>4</sub> and polycrytalline IrSi wilh different atomic composition will have different work function and lead to the different Schottky barrier height. In addition, the microstructure difference of crystallization will also affect the Schottky barrier height. Wang et al. reported that the Schottky barrier height of epitaxial PtSi/p-Si(100) diode is 0.02 eV higher than that for polycrytalline PtSi/p-Si(100) diode [11]. With regard to the ideality factor, the better diode with lower recombination current has smaller n value. The n is equal to unity for ideal diode and generally exceeds unity [12]. The higher n value of epitaxial Ir<sub>3</sub>Si<sub>4</sub>/p-Si(100) diode than polycrytalline IrSi/p-Si(100) one implies that the more interfacial states of carbon and oxygen remained exists at the Ir<sub>3</sub>Si<sub>4</sub>/p-Si(100) interface [1]. The n value degradation of epitaxial Ir<sub>3</sub>Si<sub>4</sub>/p-Si(100) diode becomes more obvious at low temperature of 60 K due to the more interfacial states.

Table II. Schottky barrier heights and ideality factors of the polycrystalline IrSi/p-Si(100) diode at different temperatures

| Temperature | Barrier height    | Ideality factor |

|-------------|-------------------|-----------------|

| (K)         | $(\phi_{b0}, eV)$ | (n)             |

| 60          | 1.10              | 0.155           |

| 70          | 1.09              | 0.157           |

| 80          | 1.08              | 0.157           |

| 90          | 1.07              | 0.158           |

| 100         | 1.07              | 0.159           |

#### 4. Conclusions

The electrical properties of epitaxial and polycrytalline Ir-silicide/p-Si(100) diodes prepared in ultra high vacuum are investigated. The average Schottky barrier height of epitaxial  $Ir_3Si_4/p$ -Si(100) diode at 60-100K is determined to be 0.177 eV, which is 0.02 eV higher than that for the polycrytalline IrSi/p-Si(100) diode.

The different barrier height is attributed to the difference of atomic arrangement at the Ir-silicide/p-Si(100) interface. This may be from the difference of phase composition and microstructure between  $Ir_3Si_4$  and IrSi silicides. The epitaxial  $Ir_3Si_4/p$ -Si(100) diode with higher n value implies that the more interfacial states exists at the  $Ir_3Si_4/p$ -Si(100) interface.

### Acknowledgements

This work was sponsored by the Ministry of Economic Affairs MOEA 88-EC-2-A-17-0203.

#### References

- [1] B.-Y. Tsaur, M.M. Weeks and P.W. Pellegrini, IEEE Electronic Dev. Lett. 9, 100 (1988).

- [2] B.-Y. Tsaur, M.M. Weeks, R. Trubiano, P.W. Pellegrini and T.-R. Yew, IEEE Electronic Dev. Lett. 9, 650 (1988).

- [3] B.-Y. Tsaur, M.J. Mcnutt, R.A. Bredthauer and R.B. Mattson, IEEE Electronic Dev. Lett. 10, 361 (1989).

- [4] B.-Y. Tsaur, C.K. Chen and B.A. Neckay, IEEE Electronic Dev. Lett. 11, 415 (1990).

- [5] P.W. Pellegrini, C.E. Ludington and M.M. Weeks, J. Appl. Phys. 67, 1417 (1990)

- [6] R.T. Tung, Phys. Rev. Lett. 52, 461 (1984).

- [7] C.K. Chung, J. Hwang, Y.H. Chang, W.J. Chen, and L.P. Wang, J. Cryst. Growth 126, 675 (1993).

- [8] C.K. Chung and J. Hwang, J. of Appl. Phys. 76, 1937 (1994).

- [9] C.K. Chung, and J. Hwang, Mat. Phys. and Chem. 43, 191 (1996).

- [10] A. Ishizaka and Y. Shiraki, J. Electrochem. Soc. 133, 666 (1986)

- [11] L.P. Wang, J.R. Yang and J. Hwang, J. of Appl. Phys. 74, 6251 (1993).

- [12] E.H. Rhoderick and R.H. Willian, Metal-Semiconductor Contact, 2<sup>nd</sup> ed., Oxford University Press, London, p. 39 (1988).